Time left 0:17:38

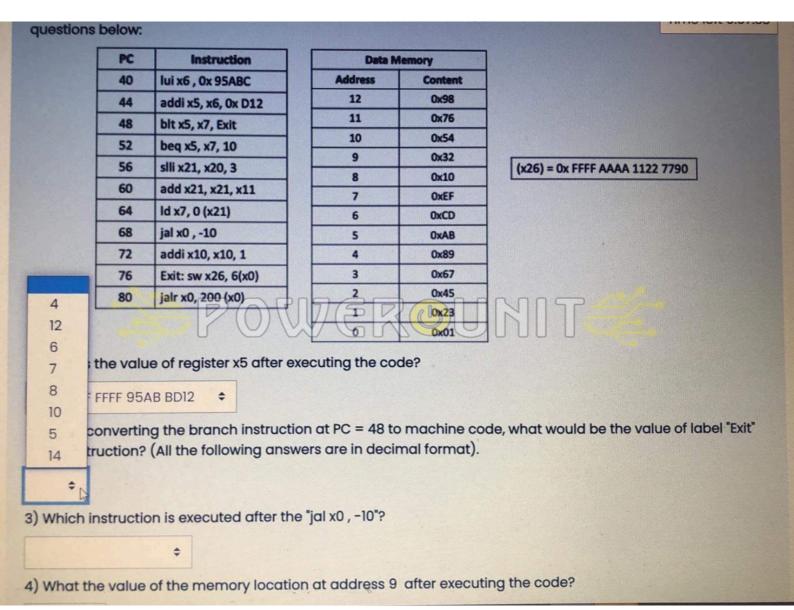

The following figure shows a RISC-V Assembly code a long with the contents of the data memory address 0 to address 12) and the contents of register x26. Accordingly, choose the correct answer for the questions below:

| PC | Instruction         |

|----|---------------------|

| 40 | lui x6 , 0x 95ABC   |

| 44 | addi x5, x6, 0x D12 |

| 48 | blt x5, x7, Exit    |

| 52 | beq x5, x7, 10      |

| 56 | slli x21, x20, 3    |

| 60 | add x21, x21, x11   |

| 64 | ld x7, 0 (x21)      |

| 68 | jal x0 ,-10         |

| 72 | addi x10, x10, 1    |

| 76 | Exit: sw x26, 6(x0) |

| 80 | jalr x0, 200 (x0)   |

| Data N  | lemory  |

|---------|---------|

| Address | Content |

| 12      | 0x98    |

| 11      | 0x76    |

| 10      | 0x54    |

| 9       | 0x32    |

| 8       | 0x10    |

| 7       | OxEF    |

| 6       | 0xCD    |

| 7/55 0  | ( [GKAB |

|         | 0x89    |

| 3       | 0x67    |

| 2       | 0x45    |

| 1       | 0x23    |

| 0       | 0x01    |

(x26) = 0x FFFF AAAA 1122 7790

1) What is the value of register x5 after executing the code?

ı,

2) When converting the branch instruction at PC = 48 to machine code, what would be the value of label "Exit" in the instruction? (All the following answers are in decimal format).

E

3) Which instruction is executed after the "jal x0, -10"?

| 30 | אווו אבז, אבט, ס    |

|----|---------------------|

| 60 | add x21, x21, x11   |

| 64 | ld x7, 0 (x21)      |

| 68 | jal x0 , -10        |

| 72 | addi x10, x10, 1    |

| 76 | Exit: sw x26, 6(x0) |

| 80 | jalr x0, 200 (x0)   |

| 0x10 |

|------|

|      |

| OxEF |

| 0xCD |

| OxAB |

| 0x89 |

| 0x67 |

| 0x45 |

| 0x23 |

| 0x01 |

|      |

(x26) = 0x FFFF AAAA 1122 7790

1) What is the value of register x5 after executing the code?

0xFFFF FFFF 95AB CD12 0x0000 0000 95AB 3D12 0xFFFF FFFF FFF9 67CE 0x0000 0000 95AB CD12

\$

instruction at PC = 48 to machine code, what would be the value of label "Exit" ving answers are in decimal format).

d after the "jal x0, -10"?

0xFFFF FFFF 95AB BD12

4) What the value of the memory location at address 9 after executing the code?

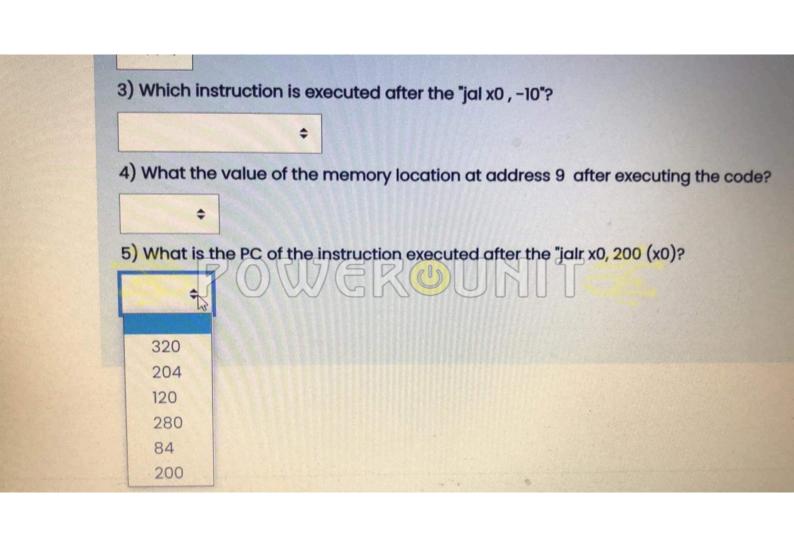

5) What is the PC of the instruction executed after the "jalr x0, 200 (x0)?

in the instruction? (All the following answers are in decimal format).

14 \$

3) Which instruction is executed after the "jal x0, -10"?

lui x6, 0x 95ABC blt x5, x7, Exit slli x21, x20, 3 addi x5, x6, 0x D12 beq x5, x7, 10 memory location at address 9 after executing the code?

DWEROUNIT

nstruction executed after the "jalr x0, 200 (x0)?

| 2) Wh<br>in the | en converting the branch instruction at PC = 48 to machine code, what would be the vainstruction? (All the following answers are in decimal format). |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14              |                                                                                                                                                      |

| 3) Wh           | ich instruction is executed after the "jal x0 , -10"?                                                                                                |

|                 | ÷                                                                                                                                                    |

|                 |                                                                                                                                                      |

| 4) Wh           | at the value of the memory location at address 9 after executing the code?                                                                           |

|                 | · LOW CWOULD                                                                                                                                         |

|                 |                                                                                                                                                      |

|                 | ne PC of the instruction executed after the "jalr x0, 200 (x0)?                                                                                      |

| 0x              |                                                                                                                                                      |

| Ox              |                                                                                                                                                      |

|                 | 90                                                                                                                                                   |

| 0x<br>0x        | 11<br>90<br>12                                                                                                                                       |

Time left 0:55:37

Given a machine-code RISC-V instruction is divided as in the figure below, choose the possible assembly instruction which matches the machine-code. Notice that the "?" indicates that the bit could be either "0" or "1".

0000000 00111 00101 7?? 00100 ???????

- O sd x7, 2 (x5)

- O bgeu x7, x5, 2

- O bge x5, x7, 2

- O bne x7, x5, 4

- O blt x5, x7, 4

- sb x5, 4 (x7)

POWEROUNIT

Computerl and Computer2 use the <u>exact same CPU</u>. The types of instructions supported by the CPU and their respective clock per instruction (CPI) are given in the top table. When running ProgramX on both computers, the numbers of instructions of each type are given in the bottom table. Which computer is faster when running ProgramX and by how much?

| Instruction Type | Α | В | С | D | Ε | F |

|------------------|---|---|---|---|---|---|

| CPI              | 2 | 3 | 2 | 1 | 3 | 5 |

| Instruction Type  | Α | В | С | D | Ε | F |

|-------------------|---|---|---|---|---|---|

| ICi for Computer1 | 4 | 0 | 0 | 1 | 1 | 3 |

| ICi for Computer2 | 0 | 0 | 4 | 1 | 2 | 6 |

- Both computers have the same performance

- O Computer1 is 1.3333 times faster than Computer2

- No enough information

- Computer1 is 1.6666 times faster than Computer2

- O Computer2 is 1.66666 times faster than Computer1

- O Computer2 is 1.1111 times faster than Computer1

- Computer1 is 1.1111 times faster than Computer2

- O Computer2 is 1.3333 times faster than Computer1

| A computer designer replaced a processor which consists of 3 stages that consists of 8 stages. Which great idea is implied in this scenario? | war a new processor |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Use Abstraction to Simplify Design     Make Common Case Fast                                                                                 |                     |

| O Performance via Parallelism                                                                                                                | B                   |

| O Dependability via Redundancy                                                                                                               |                     |

| O Performance via Prediction                                                                                                                 |                     |

| O Hierarchy of Memories                                                                                                                      |                     |

| O Performance via Pipelining                                                                                                                 |                     |

| Design for Moore's Law                                                                                                                       |                     |

|                                                                                                                                              |                     |

|                                                                                                                                              |                     |

|                                                                                                                                              |                     |

|                                                                                                                                              |                     |

| Whic | h of the following statements is correct regarding classes of computers?                                     |

|------|--------------------------------------------------------------------------------------------------------------|

|      | can choose multiple answer; however wrong answers will result in grade action)                               |

|      | Server computers are normally more reliable than Personal computers                                          |

| 72   | Super computers are the fastest class  Parallelism to improve performance is only used in Embedded computers |

|      | Personal computers have stringent budgets for performance, power, and performance                            |

| 0    | Server computers come with built-in specialized software                                                     |

|      |                                                                                                              |

|      |                                                                                                              |

## CPUI and CPU2 are running ProgramX. Given the following information, answer the question below:

- For CPU1, the number of CPU clock cycles is 100.

- For CPU2, the total instruction count is 15 and the weighted average CPI is 5.

- CPU2 is 2-times faster than CPUI.

What is the relation between clock rate of CPU1 (i.e. R1) and clock rate of CPU2 (i.e. R2)?

- $\bigcirc$  R1 = 2 x R2

- O RI = (8 x R2) ÷3 POWEROUNIT

- O R2 = 1.5 x R1

- R2 = 0.75 x R1

- O R2 = 2 x R1

- O R1 = 0.75 x R2

- $\bigcirc$  R2 = (8 x R1)÷3

- O RI = 1.5 x R2

Clear my choice

IIITIE IEIL U.ZZ.Z

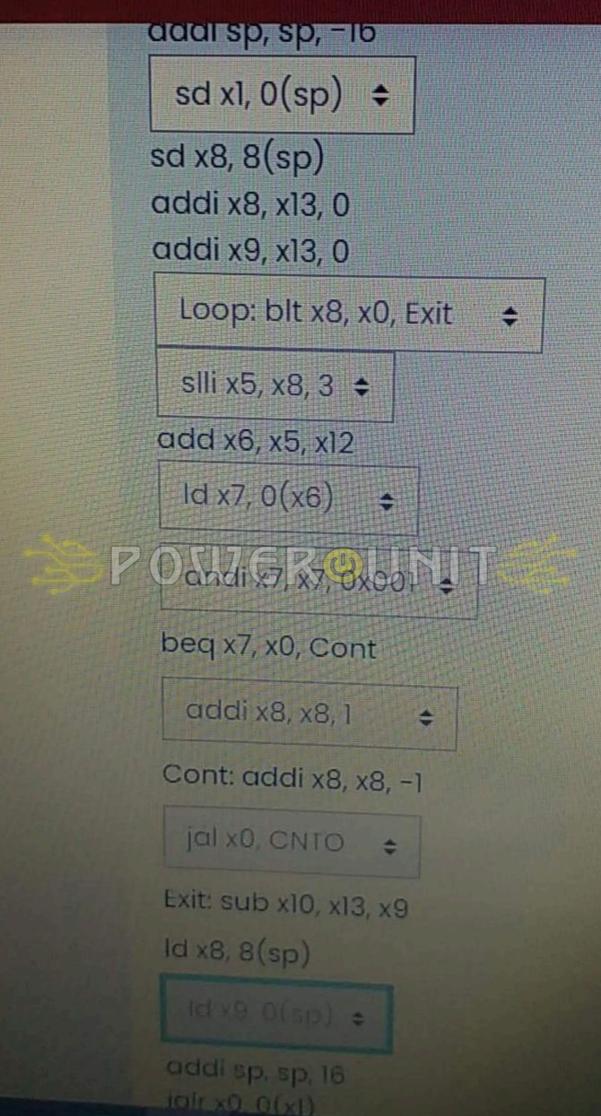

The following C-code is <u>partially</u> converted to RISC-V Assembly language. Use register x12 for the <u>base address</u> of array "Num", register x13 for variable "m", register x8 for variable "i", register x9 for variable "count". The returned value should be mapped to x10. The table below includes the saved and temporary registers.

Hint: A number is odd (فردي) if its least significant bit is one.

dva alan)

| Saved Registers     | x8 to x9, x18 to x27 |

|---------------------|----------------------|

| Temporary Registers |                      |

```

long long int CNTO (long long int Num [], long long int m)

{

long long int count = m;

for (long long int i = m; i = );

if (Num[i] is odd)

count--;

return (m - count);

}

You need to select the correct missing RISC-V instructions from the drop-down lists:

CNTO:

addi sp, sp, -16

```

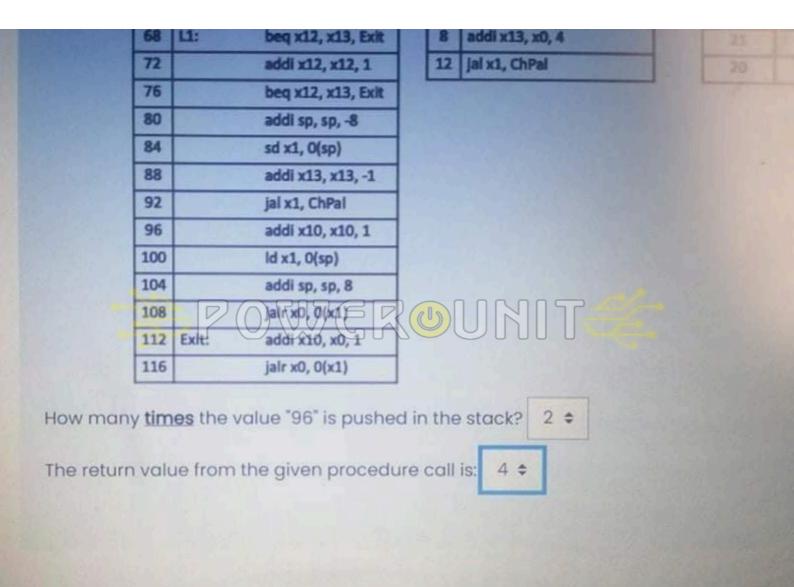

The following tables include: Non-leaf procedure "ChPal" written in RISC-V assembly language, a procedure call, and memory contents. The "ChPal" procedure has three arguments mapped to registers x11, x12, and x13. The return value of the procedure is mapped to register x10. Accordingly, answer the questions below:

Note: The memory contents are given as characters for simplicity.

|     | Procedure "ChPal"       |

|-----|-------------------------|

| PC  | Instruction             |

| 40  | ChPal: add x5, x12, x11 |

| 44  | lbu x5, 0(x5)           |

| 48  | add x6, x13, x11        |

| 52  | lbu x6, 0(x6)           |

| 56  | beq x5, x6, L1          |

| 60  | addi x10, x0, 0         |

| 64  | jalr x0, 0(k1)          |

| 68  | L1: beq x12, x13, Exit  |

| 72  | addi x12, x12, 1        |

| 76  | beq x12, x13, Exit      |

| 80  | addi sp, sp, -8         |

| 84  | sd x1, 0(sp)            |

| 88  | addi x13, x13, -1       |

| 92  | jal x1, ChPal           |

| 96  | addi x10, x10, 1        |

| 100 | id x1, 0(sp)            |

| 104 | addi sp, sp, 8          |

| 108 | jalr x0, 0(x1)          |

| 112 | Exit: addi x10, x0, 1   |

| 116 | jalr x0, 0(x1)          |

|    | Procedure Call     |

|----|--------------------|

| PC | Instruction        |

| 0  | addi x11, x0, 20   |

| 4  | addi x 12, x0, (C) |

| 8  | addix13, kb, a     |

| 12 | jal x1, ChPal      |

| Address | Memory Contents |

|---------|-----------------|

| 24      | 4               |

| 23.     | '0'             |

| 22      | Y               |

| U 21    | 'o'             |

| 20      | Y               |

| Given a processor that performs only two operations: Multiply (70% of the operations)   |

|-----------------------------------------------------------------------------------------|

| and Shift (30% of the operations). The time of every Multiply operation is 20ns and the |

| time of every Shift operation is 5ns. Which of the following design changes is          |

| considered an example of "making the common case fast to improve performance"?          |

|                                                                                         |

- O None of the answers

- Composition of the same and change Shift time to Ins

- Change Multiply time to 22ns and Shift time to 3ns

- O Change Multiple time to 10ns and Shift time to 40ns

- Change Multiple time to 15ns and Shift time to 10ns