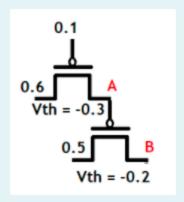

Given that initially the voltage at nodes A and B is IV Select from the given options the voltages at Node A and B after connecting the transistors to voltage sources with the values displayed on each transistor.

Time left 0:58:33

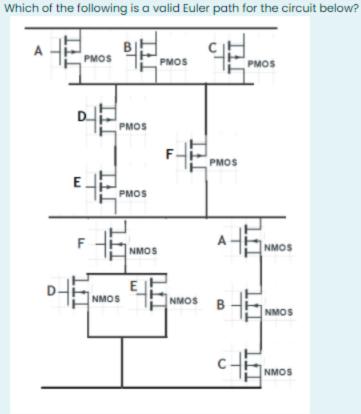

- ABCEDF

- DEFABC

- O FDEABC

- O None of the other options

- O DECBAF

116 1611 0.24.00

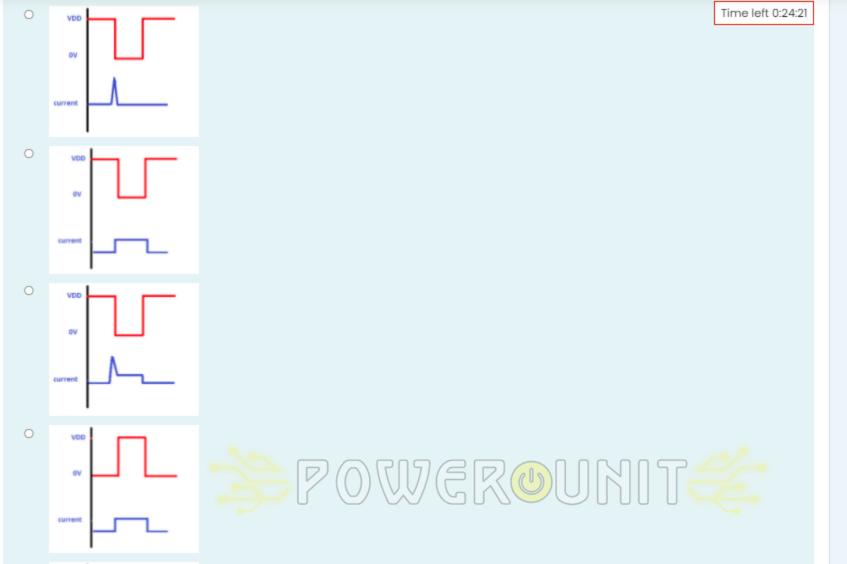

Which of the following figures represents the current of the NMOS Transistor in the NMOS resistive load inverter?

Note:

1- The red curve represents the input voltage

2- The blue curve represents the absolute value of the current

3- Despite showing the output current as a square wave, please assume that these transitions does not take 0 time and depends on the circuit parameters.

Question 2 Not yet

answered

Marked out of

1.00

♥ Flag

question

Select the needed fabrication steps to fabricate **the Nwell** and Order them. The steps sequence will follow the alphabetical order, **A** will be assigned to the first step, **B** to the second step and so on. In case the step is not needed the you have to select **No** from the available options.

## Select All Correct Statements

- Increasing Temperature will reduce the ON current of the transistor.

- □ Reducing tox of the PMOS transistor will make the PMOS transistor slower.

☑ Increasing the VDD will decrease the OFF current of the NIMOS transistor.

- Decreasing VDD will make the transistor slower.

Given that the input values are ABCD = 1100 . What is the total gate capacitance seen by input **A** Given that the gate capacitation unit size NMOS and PMOS transistors is C<sub>q</sub>

Notel: Assume all ON transistors operate in Linear mode

Note2: Round the Capacitance to the nearest integer.

- C<sub>g</sub>

- 0 2\*0

- O 3\*C

- 4\*C<sub>g</sub>

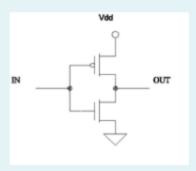

The following figure shows the schematic of the CMOS inverter. Assuming  $V_{DD}$ =1.2, and  $V_{th,p}$ =0.3V and  $V_{th,p}$ = -0.4V. What is the mode of operation for the PMOS and NMOS transistors when  $V_{in}$  = 0.9V and  $V_{out}$  =0.3V.

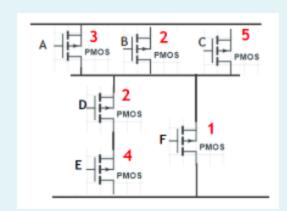

The circuit below represents the implementation of function OUT. The sizes of the transistors in the pull up network is shown in red color beside each transistor. What is the worst case delay of the pull up network in terms of Rn given that the mobility of the electrons is 4 times the mobility of the holes.

## Note: Round the number to the nearest integer.

- O Rn

- 2 \* Rn

- 3 \* Rn

- 4 \* Rn

- 5 \* Rn

- 6 \* Rn

- 7 \* Rn