## Logic and Computer Design Fundamentals Chapter 1 – Digital Systems and Information

**Charles Kime & Thomas Kaminski**

© 2008 Pearson Education, Inc. (Hyperlinks are active in View Show mode)

Updated thoroughly by Dr. Waleed Dweik

#### **Overview**

- Digital Systems, Computers, and Beyond

- Information Representation

- Number Systems [binary, octal and hexadecimal]

- Base Conversion

- Decimal Codes [BCD (binary coded decimal)]

- Alphanumeric Codes

- Parity Bit

- Gray Codes

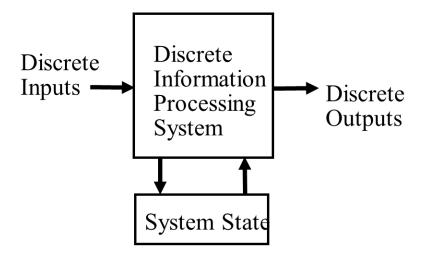

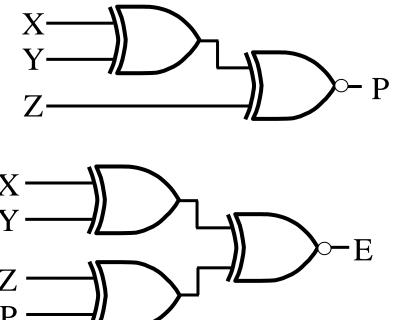

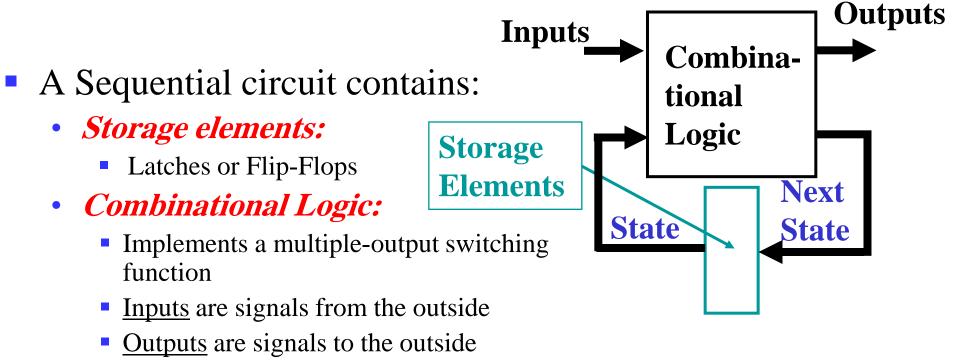

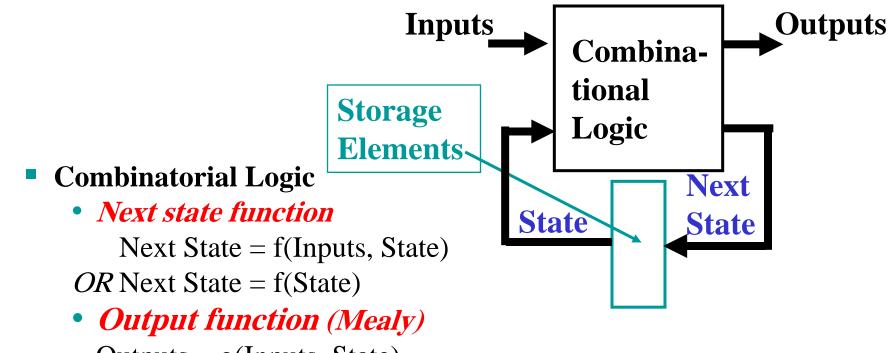

## DIGITAL & COMPUTER SYSTEMS - Digital System

- Takes a set of <u>discrete</u> information <u>inputs</u> and discrete internal information (<u>system state</u>) and generates a set of <u>discrete</u> information <u>outputs</u>.

- Digits (Latin word for fingers) : Discrete numeric elements

- Logic : Circuits that operate on a set of two elements with values 0 (False), 1 (True)

- Computers are digital logic circuits

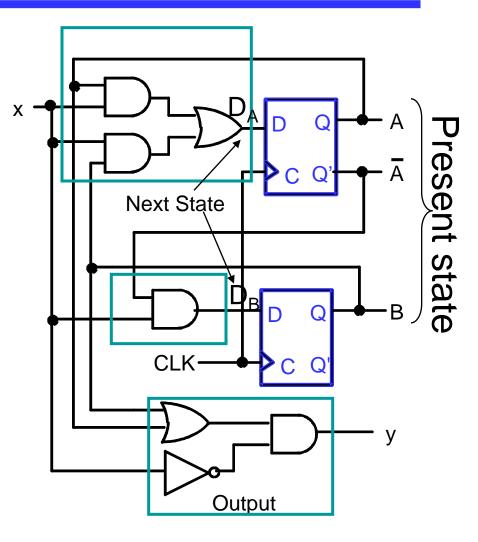

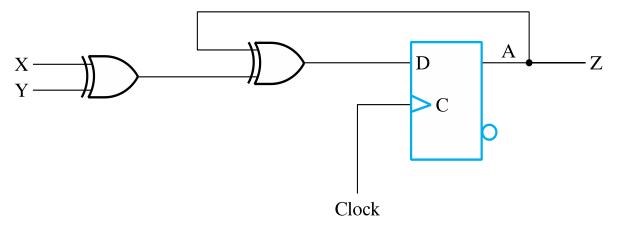

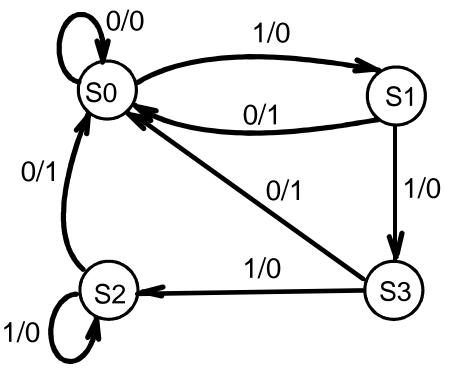

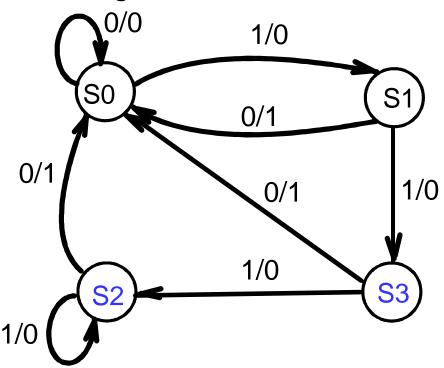

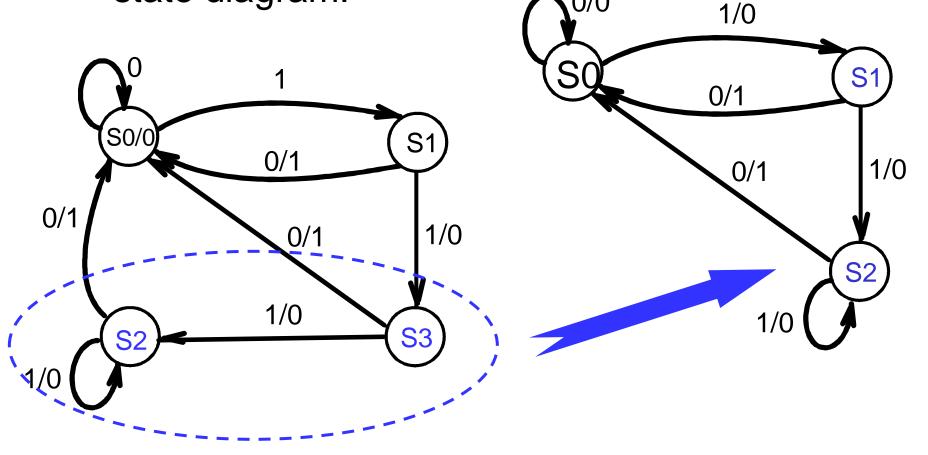

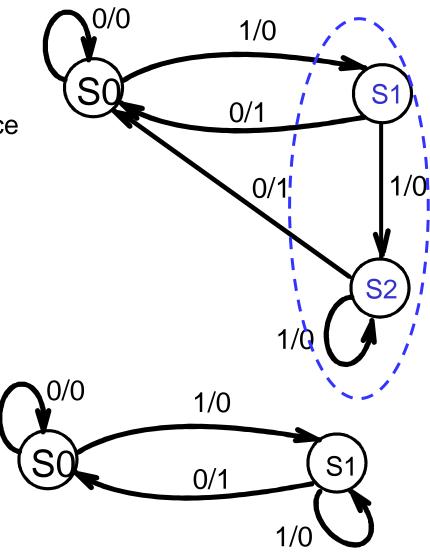

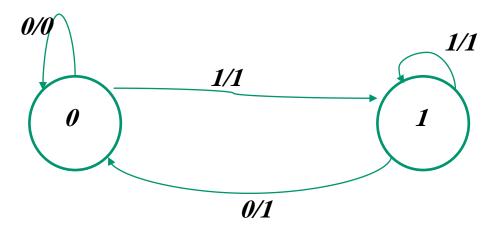

### **Types of Digital Systems**

- No state present

- Combinational Logic System

- Output = Function(Input)

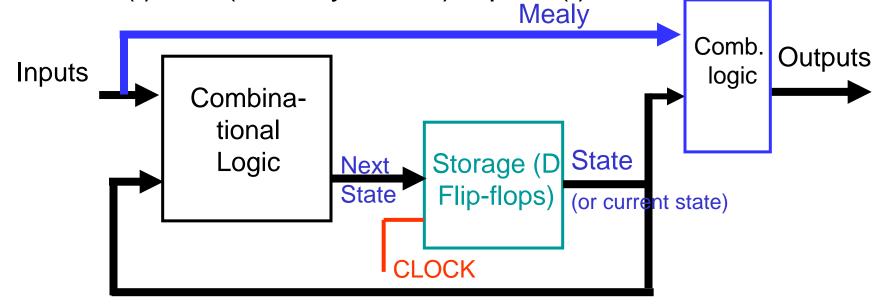

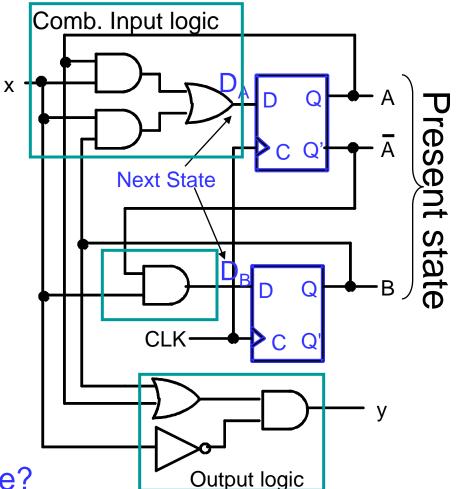

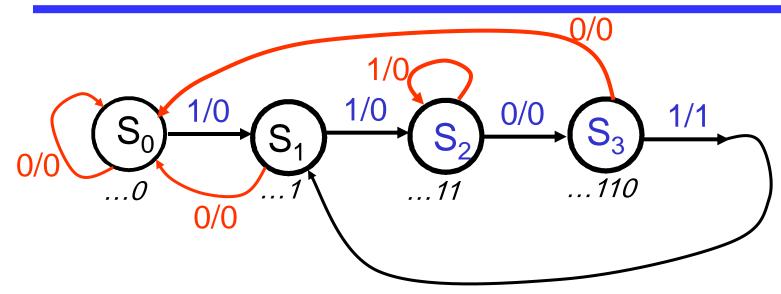

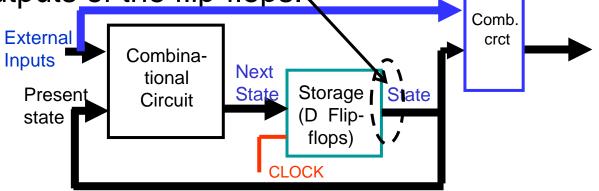

- State present

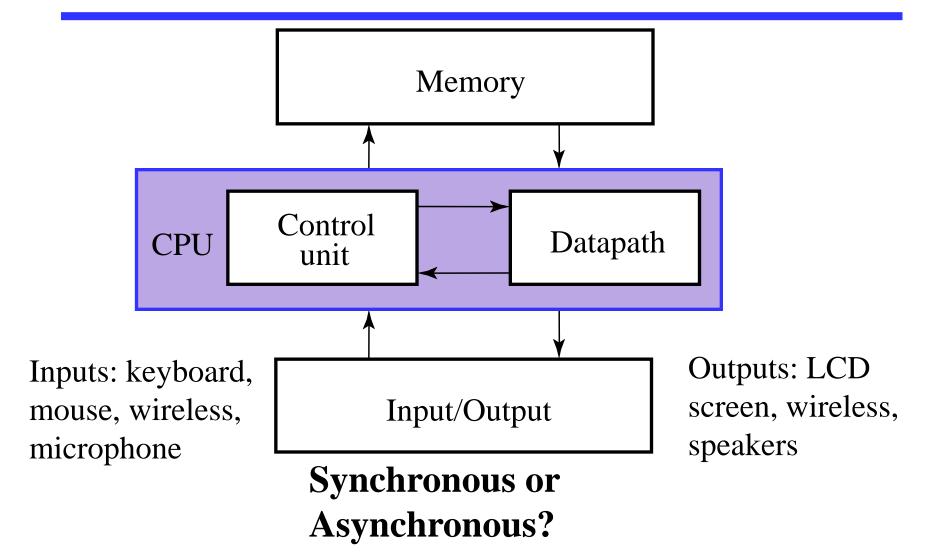

- <u>Synchronous</u> Sequential System: State updated at discrete times

- <u>Asynchronous</u> Sequential System: State updated at any time

- State = Function (State, Input)

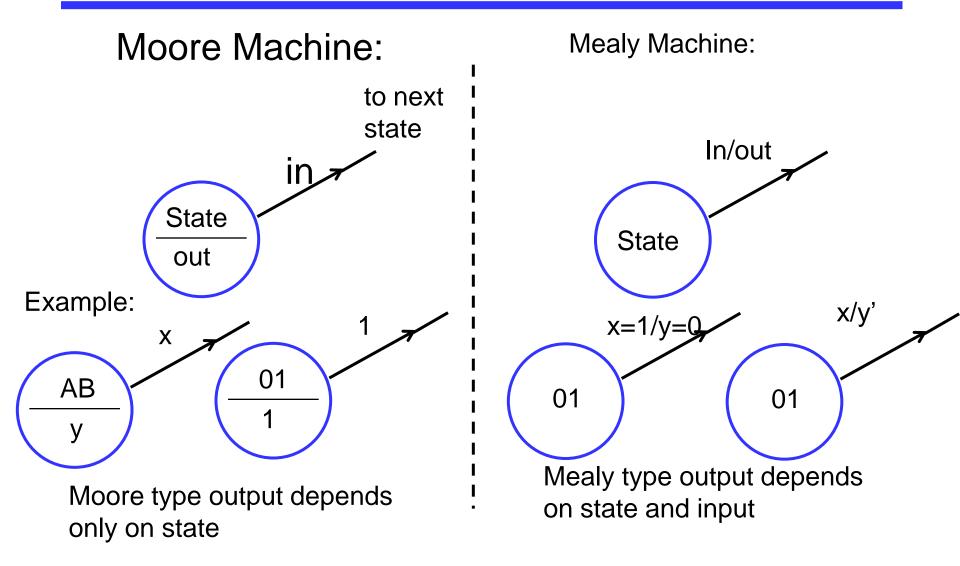

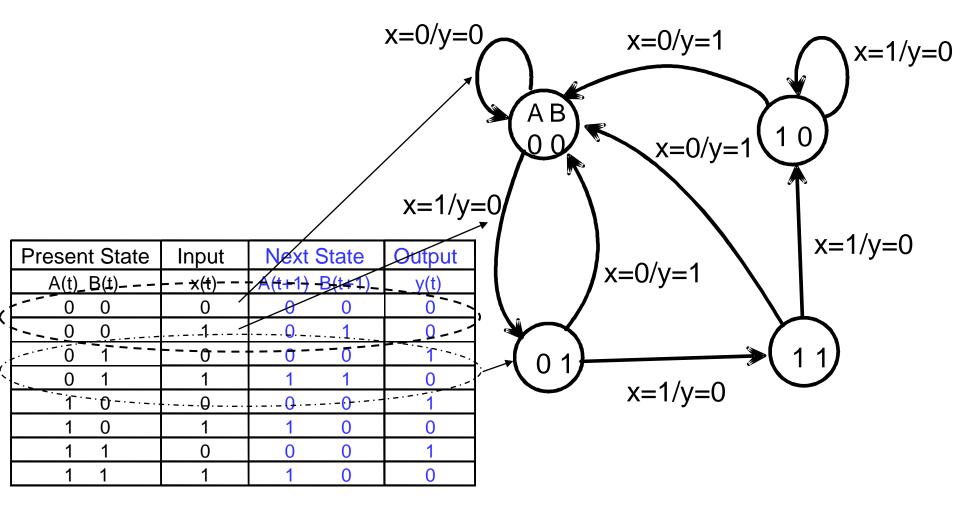

Moore

• Output = Function (State) or Function (State, Input)

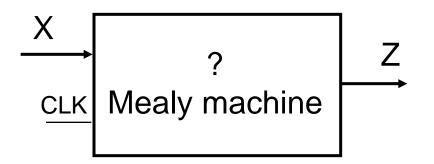

Mealy

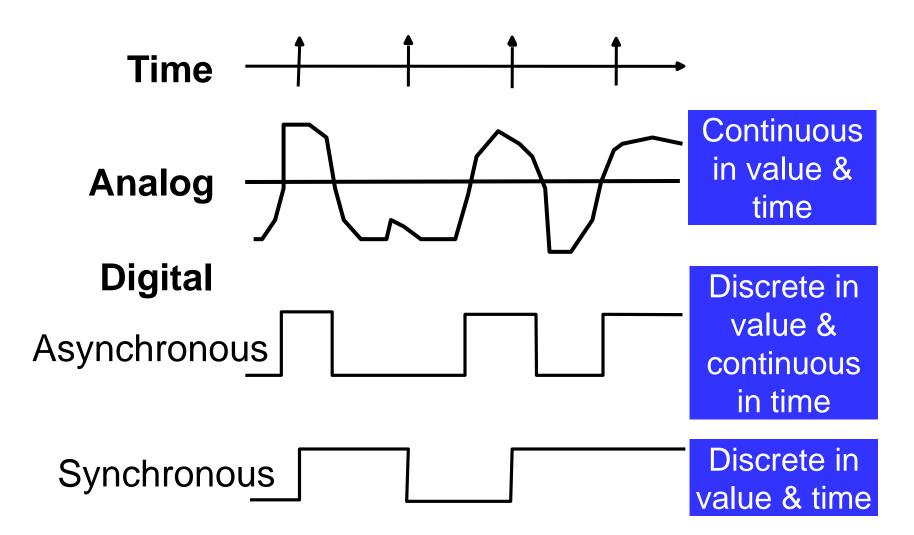

#### **Signal Examples Over Time**

#### **Digital System Example**

A Digital Counter (e. g., odometer):

$$\begin{array}{cccc} \text{Count Up} & \longrightarrow & 0 & 0 & 1 & 3 & 5 & 6 & 4 \\ \text{Reset} & \longrightarrow & 0 & 0 & 1 & 3 & 5 & 6 & 4 \end{array}$$

Inputs:Count Up, ResetOutputs:Visual DisplayState:"Value" of stored digits

Synchronous or Asynchronous?

#### **Digital Computer Example**

#### And Beyond – Embedded Systems

- Computers as integral parts of other products

- Examples of embedded computers

- Microcomputers

- Microcontrollers

- Digital signal processors

- Examples of embedded systems applications

| Cell phones | Dishwashers                |

|-------------|----------------------------|

| Automobiles | Flat Panel TVs             |

| Video games | Global Positioning Systems |

| Copiers     |                            |

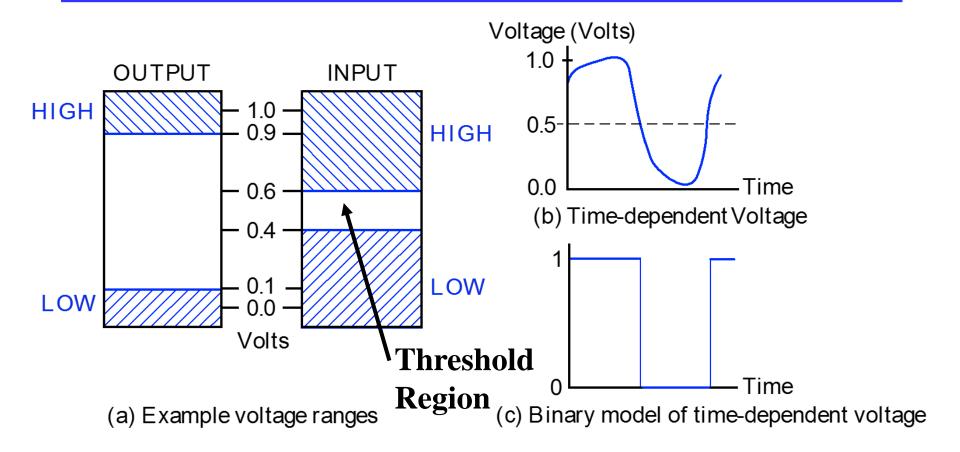

#### **INFORMATION REPRESENTATION - Signals**

- Information variables represented by physical quantities.

- For digital systems, the variables take on *discrete* values.

- Two level, or <u>binary</u> values are the <u>most prevalent</u> values in digital systems.

- Binary systems have higher immunity to noise.

- Binary values are represented abstractly by:

- digits 0 and 1

- words (symbols) False (F) and True (T)

- words (symbols) Low (L) and High (H)

- and words On and Off.

- Binary values are represented by values or ranges of values of physical quantities.

### **Binary Values: Other Physical Quantities**

- What are other physical quantities represent 0 and 1?

- CPU  $\rightarrow$  Voltage

- Disk → Magnetic Field Direction

- CD → Surface Pits/Light

- Dynamic RAM → Electrical Charge stored in capacitors

### Signal Example – Physical Quantity: Voltage

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

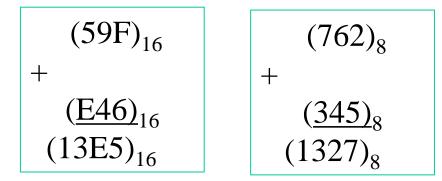

#### NUMBER SYSTEMS – Representation

- Positive radix, positional number systems

- A number with <u>radix r</u> is represented by a string of digits:

$$A_{n-1}A_{n-2} \dots A_1A_0 \dots A_{-1}A_{-2} \dots A_{-m+1}A_{-m}$$

in which  $0 \le A_i < r$  and . is the *radix point*

#### • *i* represents the position of the coefficient

- *r<sup>i</sup>* represents the weight by which the coefficient is multiplied

- $A_{n-1}$  is the most significant digit (MSD) and  $A_{-m}$  is the least significant digit (LSD)

- The string of digits represents the power series:

$$(Number)_{r} = \left(\sum_{i=0}^{n-1} A_{i}r^{i}\right) + \left(\sum_{j=-m}^{-1} A_{j}r^{j}\right)$$

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc. Integer Portion Fraction Portion Chapter 1

13

#### **Number Systems – Examples**

|              | General         | Decimal | Binary  |

|--------------|-----------------|---------|---------|

| Radix (Base) | r               | 10      | 2       |

| Digits       | 0 => r - 1      | 0 => 9  | 0 => 1  |

| 0            | r <sup>0</sup>  | 1       | 1       |

| 1            | $\mathbf{r}^1$  | 10      | 2       |

| 2            | $\mathbf{r}^2$  | 100     | 4       |

| 3            | r <sup>3</sup>  | 1000    | 8       |

| Powers of 4  | r <sup>4</sup>  | 10,000  | 16      |

| Radix 5      | r <sup>5</sup>  | 100,000 | 32      |

| -1           | r <sup>-1</sup> | 0.1     | 0.5     |

| -2           | r -2            | 0.01    | 0.25    |

| -3           | r <sup>-3</sup> | 0.001   | 0.125   |

| -4           | r -4            | 0.0001  | 0.0625  |

| -5           | r <sup>-5</sup> | 0.00001 | 0.03125 |

•  $(403)_5 = 4 \times 5^2 + 0 \times 5^1 + 3 \times 5^0 = (103)_{10}$

#### • $(103)_{10} = 1 \times 10^2 + 0 \times 10^1 + 3 \times 10^0 = 103$

#### **BASE CONVERSION - Positive Powers of 2**

#### Useful for Base Conversion

| Exponent | Value |

|----------|-------|

| 0        | 1     |

| 1        | 2     |

| 2        | 4     |

| 3        | 8     |

| 4        | 16    |

| 5        | 32    |

| 6        | 64    |

| 7        | 128   |

| 8        | 256   |

| 9        | 512   |

| 10       | 1024  |

| Exponent | Value     |

|----------|-----------|

| 11       | 2,048     |

| 12       | 4,096     |

| 13       | 8,192     |

| 14       | 16,384    |

| 15       | 32,768    |

| 16       | 65,536    |

| 17       | 131,072   |

| 18       | 262,144   |

| 19       | 524,288   |

| 20       | 1,048,576 |

| 21       | 2,097,152 |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Special Powers of 2**

- 2<sup>10</sup> (1024) is Kilo, denoted "K"

- 2<sup>20</sup> (1,048,576) is Mega, denoted "M"

- 2<sup>30</sup> (1,073, 741,824) is Giga, denoted "G"

- 2<sup>40</sup> (1,099,511,627,776 ) is Tera, denoted "T"

#### **Commonly Occurring Bases**

| Name        | Radix | Digits                          |

|-------------|-------|---------------------------------|

| Binary      | 2     | 0,1                             |

| Octal       | 8     | 0,1,2,3,4,5,6,7                 |

| Decimal     | 10    | 0,1,2,3,4,5,6,7,8,9             |

| Hexadecimal | 16    | 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F |

The six letters A, B, C, D, E, and F represent the digits for values 10, 11, 12, 13, 14, 15 (given in decimal), respectively, in hexadecimal. Alternatively, a, b, c, d, e, f can be used.

#### **Binary System**

- r = 2

- Digits =  $\{0, 1\}$

- Every binary digit is called a bit

- When a bit is equal to zero, it does not contribute to the value of the number

- Example:

- $(10011.101)_2 = (1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0) + (1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3})$

•

$$(10011.101)_2 = (16 + 2 + 1) + (\frac{1}{2} + \frac{1}{8}) = (19.625)_{10}$$

#### **Octal System**

- r = 8

- Digits =  $\{0, 1, 2, 3, 4, 5, 6, 7\}$

- Every digit is represented by 3-bits → More compact than binary

- Example:

•

$$(127.4)_8 = (1 \times 8^2 + 2 \times 8^1 + 7 \times 8^0) + (4 \times 8^{-1})$$

•

$$(127.4)_8 = (64 + 16 + 7) + \left(\frac{1}{2}\right) = (87.5)_{10}$$

#### **Hexadecimal System**

- r = 16

- Digits = {0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F}

- Every digit is represented by 4-bits

- Example:

- $(B65F)_{16} = (11 \times 16^3 + 6 \times 16^2 + 5 \times 16^1 + 15 \times 16^0)$

- $(B65F)_{16} = (46687)_{10}$

#### **Numbers in Different Bases**

#### Good idea to memorize!

| Decimal   | Binary   | Octal    | Hexadecimal |

|-----------|----------|----------|-------------|

| (Base 10) | (Base 2) | (Base 8) | (Base 16)   |

| 00        | 00000    | 00       | 00          |

| 01        | 00001    | 01       | 01          |

| 02        | 00010    | 02       | 02          |

| 03        | 00011    | 03       | 03          |

| 04        | 00100    | 04       | 04          |

| 05        | 00101    | 05       | 05          |

| 06        | 00110    | 06       | 06          |

| 07        | 00111    | 07       | 07          |

| 08        | 01000    | 10       | 08          |

| 09        | 01001    | 11       | 09          |

| 10        | 01010    | 12       | 0A          |

| 11        | 01011    | 13       | <b>0B</b>   |

| 12        | 01100    | 14       | <b>0</b> C  |

| 13        | 01101    | 15       | 0D          |

| 14        | 01110    | 16       | <b>0</b> E  |

| 15        | 01111    | 17       | <b>0</b> F  |

| 16        | 10000    | 20       | 10          |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 1 22

### **Converting from any Base (r) to Decimal**

$$(Number)_{r} = \left(\sum_{i=0}^{n-1} A_{i}r^{i}\right) + \left(\sum_{j=-m}^{-1} A_{j}r^{j}\right)$$

Integer Portion Fraction Portion

mugui i ui uu

$\mathbf{I}$

Example: Convert 11010<sub>2</sub> to N<sub>10</sub>:

## **Conversion from Decimal to Base (r)**

Convert the Integer Part

Convert the Fraction Part

Join the two results with a radix point

#### **Conversion Details**

#### • To Convert the Integral Part:

- Repeatedly <u>divide</u> the number by the new radix and save the <u>remainders</u> until <u>the quotient is zero</u>

- The digits for the new radix are the remainders in <u>reverse order</u> of their computation

- If the new radix is > 10, then convert all remainders > 10 to digits A, B, ...

#### • To Convert the Fractional Part:

- Repeatedly <u>multiply</u> the fraction by the new radix and save the <u>integer</u> <u>digits</u> of the results until the <u>fraction is zero or your reached the required</u> <u>number of fractional digits</u>

- The digits for the new radix are the integer digits *in order* of their computation

- If the new radix is > 10, then convert all integers > 10 to digits A, B, ...

#### Example: Convert 46.6875<sub>10</sub> To Base 2

| • C | onvert 4 | 46 to I | Base 2: |

|-----|----------|---------|---------|

|-----|----------|---------|---------|

$(46)_{10} = (101110)_2$

• Convert 0.6875 to Base 2:

$(0.6875)_{10} = (0.1011)_2$

| Division | Quotient | Remainder |     |

|----------|----------|-----------|-----|

| 46/2     | 23       | 0         | LSD |

| 23/2     | 11       | 1         |     |

| 11/2     | 5        | 1         |     |

| 5/2      | 2        | 1         |     |

| 2/2      | 1        | 0         |     |

| 1/2      | 0        | 1         | MSD |

| Multiplication | Answer |     |

|----------------|--------|-----|

| 0.6875*2       | 1.375  | MSD |

| 0.375*2        | 0.75   |     |

| 0.75*2         | 1.5    |     |

| 0.5*2          | 1.0    |     |

• Join the results together with the radix point:  $(46.6875)_{10} = (101110.1011)_2$

#### Example: Convert 153.513<sub>10</sub> To Base 8

• Convert 153 to Base 8:

$(153)_{10} = (231)_8$

| Division | Quotient | Remainder |  |

|----------|----------|-----------|--|

| 153/8    | 19       | 1         |  |

| 19/8     | 2        | 3         |  |

| 2/8      | 0        | 2         |  |

- Convert 0.513 to Base 8: (Up to 3 digits)

- Truncate:

$(0.513)_{10} = (0.406)_8$

• Round:

$(0.513)_{10} = (0.407)_8$

| Multiplication | Answer | ]   |

|----------------|--------|-----|

| 0.513*8        | 4.104  | MSD |

| 0.104*8        | 0.832  |     |

| 0.832*8        | 6.656  |     |

| 0.656*8        | 5.248  | LSD |

• Join the results together with the radix point:  $(153.513)_{10} = (231.407)_8$

#### Example: Convert 423<sub>10</sub> To Base 16

| Division | Quotient | Remainder |     |

|----------|----------|-----------|-----|

| 423/16   | 26       | 7         | LSD |

| 26/16    | 1        | 10        |     |

| 1/16     | 0        | 1         | MSD |

$(423)_{10} = (1A7)_{16}$

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Converting Decimal to Binary: Alternative Method**

- Subtract the largest power of 2 that gives a positive remainder and record the power

- Repeat, subtracting from the prior remainder and recording the power, until the remainder is zero

- Place 1's in the positions in the binary result corresponding to the powers recorded; in all other positions place 0's

#### Example: Convert 46.6875<sub>10</sub> To Base 2 Using Alternative Method

• Convert 46 to Base 2:

$(46)_{10} = (101110)_2$

• Convert 0.6875 to Base 2:

$(0.6875)_{10} = (0.1011)_2$

| Subtract | Remainder | Power |

|----------|-----------|-------|

| 46-32    | 14        | 5     |

| 14-8     | 6         | 3     |

| 6-4      | 2         | 2     |

| 2-2      | 0         | 1     |

| Subtract      | Remainder | Power |

|---------------|-----------|-------|

| 0.6875-0.5    | 0.1875    | -1    |

| 0.1875-0.125  | 0.0625    | -3    |

| 0.0625-0.0625 | 0         | -4    |

• Join the results together with the radix point:

$(46.6875)_{10} = (101110.1011)_2$

• Easier way to do it:

| Power | 6 | 5 | 4 | 3 | 2 | 1 | 0 | • | -1 | -2 | -3 | -4 |

|-------|---|---|---|---|---|---|---|---|----|----|----|----|

|       | 0 | 1 | 0 | 1 | 1 | 1 | 0 | • | 1  | 0  | 1  | 1  |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Additional Issue - Fractional Part**

- Note that in this conversion, the fractional part can become 0 as a result of the repeated multiplications

- In general, it may take many bits to get this to happen or it may never happen

- Example Problem: Convert 0.65<sub>10</sub> to N<sub>2</sub>

- 0.65 = 0.1010011001001 ...

- The fractional part begins repeating every 4 steps yielding repeating 1001 forever!

- Solution: Specify number of bits to right of radix point and <u>round</u> or <u>truncate</u> to this number

### **Checking the Conversion**

- To convert back, sum the digits times their respective powers of r

- From the prior conversion of 46.6875<sub>10</sub>

- $101110_{2} = 1 \cdot 32 + 0 \cdot 16 + 1 \cdot 8 + 1 \cdot 4 + 1 \cdot 2 + 0 \cdot 1$ = 32 + 8 + 4 + 2 = 46

- $\begin{array}{ll} 0.1011_2 & = 1/2 + 1/8 + 1/16 \\ & = 0.5000 + 0.1250 + 0.0625 \\ & = 0.6875 \end{array}$

# Octal (Hexadecimal) to Binary and Back: Method1

- Octal (Hexadecimal) to Binary:

- 1. Convert octal (hexadecimal) to decimal (Slide 23)

- 2. Covert decimal to binary (Slide 24 or Slide 29)

- Binary to Octal (Hexadecimal):

- 1. Convert binary to decimal (Slide 23)

- 2. Covert decimal to octal (hexadecimal) (Slide 24)

# Octal (Hexadecimal) to Binary and Back: Method2 (Easier)

- Octal (Hexadecimal) to Binary:

- <u>*Restate*</u> the octal (hexadecimal) as three (four) binary digits starting at the radix point and going both ways

- Binary to Octal (Hexadecimal):

- <u>*Group*</u> the binary digits into three (four) bit groups starting at the radix point and going both ways, padding with zeros as needed

- Convert each group of three (four) bits to an octal (hexadecimal) digit

| Octal  | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| Binary | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| Hexadecimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|-------------|------|------|------|------|------|------|------|------|

| Binary      | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

| Hexadecimal | 8    | 9    | А    | В    | С    | D    | Е    | F    |

| Binary      | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 1 34

#### **Examples**

- $(673.12)_8 = (110\ 111\ 011\ .\ 001\ 010)_2$

- $(3A6.C)_{16} = (0011\ 1010\ 0110\ .\ 1100)_2$

- $(10110001101011.1111000001)_2 = (?)_8$

$(10/110/001/101/011.111/100/000/1)_2 = (26153.7404)_8$

•  $(10110001101011.1111000001)_2 = (?)_{16}$ (10/1100/0110/1011.1111/0000/01)\_2 = (2C6B.F04)\_{16}

#### **Octal to Hexadecimal via Binary**

- Convert octal to binary

- Use groups of <u>four bits</u> and convert to hexadecimal digits

- Example: Octal to Binary to Hexadecimal

```

(635.177)_{8} \downarrow (110\ 011\ 101\ .\ 001\ 111\ 111)_{2} \downarrow (1/1001/1101\ .\ 0011/1111/1)_{2} \downarrow (1/1001/1101\ .\ 0011/1111/1)_{2} \downarrow (19D.3F8)_{16}

```

### **One last Conversion Example**

• Given that  $(365)_r = (194)_{10}$ , compute the value of r?

$$3 \times r^2 + 6 \times r^1 + 5 \times r^0 = 194$$

$3r^2 + 6r + 5 = 194$

- $3r^2 + 6r 189 = 0$

- $r^2 + 2r 63 = 0$

- (r-7)(r+9) = 0

- r = 7

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

## **Binary Numbers and Binary Coding**

#### Flexibility of representation

- Within constraints below, can assign any binary combination (called a *code word*) to any data as long as data is uniquely encoded

- Information Types

- <u>Numeric</u>

- Must represent range of data needed

- Very desirable to represent data such that simple, straightforward computation for common arithmetic operations permitted

- Tight relation to binary numbers

- Non-numeric

- Greater flexibility since arithmetic operations not applied

- Not tied to binary numbers

## **Non-numeric Binary Codes**

- Given *n* binary digits (called <u>bits</u>), a <u>binary code</u> is a mapping from a set of <u>represented elements</u> to a subset of the 2<sup>n</sup> binary numbers.

- Example: A binary code for the seven colors of the rainbow

- Code 100 is not used

| Color  | Binary Number |

|--------|---------------|

| Red    | 000           |

| Orange | 001           |

| Yellow | 010           |

| Green  | 011           |

| Blue   | 101           |

| Indigo | 110           |

| Violet | 111           |

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

### **Number of Bits Required**

Given *M* elements to be represented by a binary code, the minimum number of bits, *n*, needed, satisfies the following relationships:

$$2^n \ge M > 2^{n-1}$$

$n = [log_2 M]$ , where [x] is called

the *ceiling function*, is the integer greater than or equal to *x*.

Example: How many bits are required to represent <u>decimal</u> <u>digits</u> with a binary code?

$$M = 10$$

$$n = [log_2 10] = [3.33] = 4$$

### Number of Elements Represented

- Given *n* digits in radix *r*, there are  $r^n$  distinct elements that can be represented.

- But, you can represent m elements,  $m \leq r^n$  Examples:

- You can represent 4 elements in radix r = 2 with n = 2 digits: (00, 01, 10, 11).

- You can represent 4 elements in radix r = 2 with n = 4 digits: (0001, 0010, 0100, 1000).

- This second code is called a "<u>one hot</u>" code.

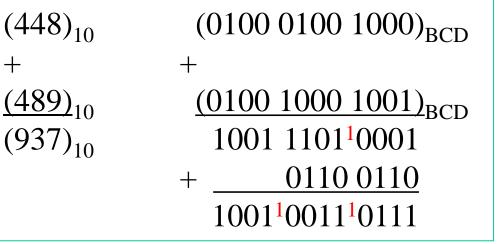

## DECIMAL CODES - Binary Codes for Decimal Digits

There are over 8,000 ways that you can chose 10 elements from the 16 binary numbers of 4 bits. A few are useful:

| Decimal | 8, 4, 2, 1 | Excess 3 | 8, 4, -2, -1 | Gray |

|---------|------------|----------|--------------|------|

| 0       | 0000       | 0011     | 0000         | 0000 |

| 1       | 0001       | 0100     | 0111         | 0001 |

| 2       | 0010       | 0101     | 0110         | 0011 |

| 3       | 0011       | 0110     | 0101         | 0010 |

| 4       | 0100       | 0111     | 0100         | 0110 |

| 5       | 0101       | 1000     | 1011         | 1110 |

| 6       | 0110       | 1001     | 1010         | 1010 |

| 7       | 0111       | 1010     | 1001         | 1011 |

| 8       | 1000       | 1011     | 1000         | 1001 |

| 9       | 1001       | 1100     | 1111         | 1000 |

## **Binary Coded Decimal (BCD)**

- Numeric code

- The BCD code is the 8, 4, 2, 1 code

- 8, 4, 2, and 1 are weights  $\rightarrow$  BCD is a *weighted* code

- This code is the simplest, most intuitive binary code for decimal digits and uses the same powers of 2 as a binary number, *but only encodes the first ten values from 0 to 9*

- Example: 1001 (9) = 1000 (8) + 0001 (1)

- How many "invalid" code words are there?

- Answer: 6

- What are the "invalid" code words?

- Answer: 1010, 1011, 1100, 1101, 1110, 1111

## Warning: Conversion or Coding?

Do NOT mix up *conversion* of a decimal number to a binary number with *coding* a decimal number with a BINARY CODE.

## 13<sub>10</sub> = 1101<sub>2</sub> (This is <u>conversion</u>)

## • 13 $\Leftrightarrow$ 0001|0011 (This is <u>coding</u>)

### Excess 3 Code and 8, 4, -2, -1 Code

- What interesting property is common to these two codes?

- Answer: Both codes have the property that the codes for 0 and 9, 1 and 8, etc. can be obtained from each other by replacing the 0's with the 1's and vice-versa. Such a code is sometimes called a *complement code*.

| Decimal | Excess 3 | 8, 4, -2, -1 |

|---------|----------|--------------|

| 0       | 0011     | 0000         |

| 1       | 0100     | 0111         |

| 2       | 0101     | 0110         |

| 3       | 0110     | 0101         |

| 4       | 0111     | 0100         |

| 5       | 1000     | 1011         |

| 6       | 1001     | 1010         |

| 7       | 1010     | 1001         |

| 8       | 1011     | 1000         |

| 9       | 1100     | 1111         |

#### ALPHANUMERIC CODES - ASCII Character Codes

- Non-numeric code

- ASCII stands for American Standard Code for Information Interchange (Refer to Table 1-5 in the text)

- This code is a popular code used to represent information sent as character-based data. It uses 7bits (i.e. 128 characters) to represent:

- 95 Graphic printing characters

- 33 Non-printing characters

### **ASCII Code Table**

|             | Least Significant |     |     |     |     |     |     |      |       |      |      |     |     |    |    |    |     |

|-------------|-------------------|-----|-----|-----|-----|-----|-----|------|-------|------|------|-----|-----|----|----|----|-----|

|             |                   |     |     |     |     |     | A   | SCII | : Cod | le C | hart |     |     |    |    |    |     |

|             |                   | 0   | 1   | 2   | 3   | 4   | 5   | 6    | 7     | 8    | 9    | A   | В   | С  | D  | Е  | F   |

|             | 0                 | NUL | SOH | STX | ETX | EOT | ENQ | ACK  | BEL   | BS   | HT   | LF  | VT  | FF | CR | S0 | SI  |

| ant         | 1                 | DLE | DC1 | DC2 | DC3 | DC4 | NAK | SYN  | ETB   | CAN  | ЕМ   | SUB | ESC | FS | GS | RS | US  |

| Significant | 2                 |     | !   |     | #   | \$  | %   | &    |       | (    | )    | *   | +   | ,  | -  | •  | /   |

| <b>B</b>    | 3                 | 0   | 1   | 2   | 3   | 4   | 5   | 6    | 7     | 8    | 9    |     | ;   | ٨  | =  | ٨  | ?   |

| t Si        | 4                 | 0   | Α   | В   | С   | D   | Ε   | F    | G     | Η    | I    | J   | Κ   | L  | М  | Ν  | 0   |

| Most        | 5                 | Р   | Q   | R   | S   | Т   | U   | V    | W     | Х    | Y    | Z   | ]   | \  | ]  | ^  | _   |

|             | 6                 | `   | а   | b   | с   | d   | е   | f    | g     | h    | i    | j   | k   | ι  | m  | n  | 0   |

|             | 7                 | р   | q   | r   | S   | t   | u   | V    | W     | X    | у    | z   | {   |    | }  | 2  | DEL |

## **ASCII Character Codes**

- Graphic printing characters

- 26 upper case letters (A-Z)

- 26 lower case letters (a-z)

- 10 numerals (0-9)

- 33 special characters (e.g. %, @, \$)

- Non-printing characters

- Format effectors: used for text format (e.g. BS = Backspace, CR = carriage return)

- Information separators: used to separate the data into paragraphs and pages (e.g. RS = record separator, FS = file separator)

- Communication control characters (e.g. STX and ETX start and end text areas).

## **ASCII** Properties

- ASCII has some interesting properties:

- Digits 0 to 9 span Hexadecimal values  $30_{16}$  to  $39_{16}$

- Upper case A-Z span  $41_{16}$  to  $5A_{16}$

- Lower case a-z span  $61_{16}$  to  $7A_{16}$

- Lower to upper case translation (and vice versa) occurs by flipping bit 6

## UNICODE

- UNICODE extends ASCII to 65,536 universal characters codes:

- Non-numeric

- For encoding characters in world languages

- Available in many modern applications

- 2 byte (16-bit) code words

## **PARITY BIT Error-Detection Codes**

- Non-numeric

- *Redundancy* (e.g. extra information), in the form of extra bits, can be incorporated into binary code words to detect and correct errors

- A simple form of redundancy is *parity*, an extra bit appended onto the code word to make the number of 1's odd or even. Parity can detect all single-bit errors and some multiple-bit errors

- A code word has *even parity* if the number of 1's in the code word is even

- A code word has *odd parity* if the number of 1's in the code word is odd

## **4-Bit Parity Code Example**

#### • Fill in the even and odd parity bits:

| Even Parity Message | Odd Parity Message |

|---------------------|--------------------|

| 0000                | <u>0001</u>        |

| 001 <u>1</u>        | <u>0010</u>        |

| 010 <u>1</u>        | 010 <u>0</u>       |

| 011 <u>0</u>        | 011 <u>1</u>       |

| 100 <u>1</u>        | 100 <u>0</u>       |

| 101 <u>0</u>        | 101 <u>1</u>       |

| 110 <u>0</u>        | 110 <u>1</u>       |

| 111 <u>1</u>        | <u>1110</u>        |

The code word "1111" has <u>even parity</u> and the code word "1110" has <u>odd parity</u>. Both can be used to represent the same 3-bit data

# Logic and Computer Design Fundamentals Chapter 2 – Combinational Logic Circuits

**Part 1 – Gate Circuits and Boolean Equations**

**Charles Kime & Thomas Kaminski**

© 2008 Pearson Education, Inc. (Hyperlinks are active in View Show mode)

Updated by Dr. Waleed Dweik

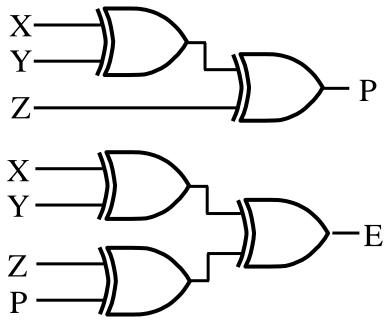

# **Combinational Logic Circuits**

- Digital (logic) circuits are hardware components that manipulate binary information.

- Integrated circuits: transistors and interconnections.

- Basic circuits is referred to as *logic gates*

- The outputs of gates are applied to the inputs of other gates to form a digital circuit

- Combinational? Later...

## Overview

#### Part 1 – Gate Circuits and Boolean Equations

- Binary Logic and Gates

- Boolean Algebra

- Standard Forms

#### Part 2 – Circuit Optimization

- Two-Level Optimization

- Map Manipulation

- Practical Optimization (Espresso)

- Multi-Level Circuit Optimization

#### Part 3 – Additional Gates and Circuits

- Other Gate Types

- Exclusive-OR Operator and Gates

- High-Impedance Outputs

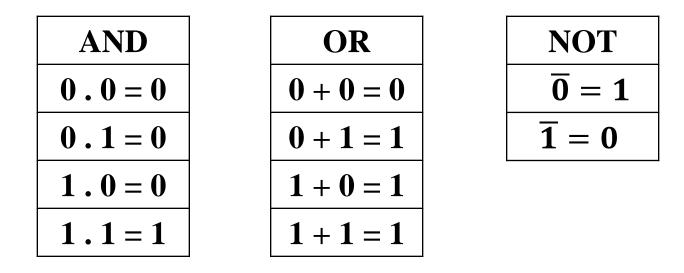

# **Binary Logic and Gates**

- Binary variables take on one of two values

- Logical operators operate on binary values and binary variables

- Basic logical operators are the logic functions AND, OR and NOT

- Logic gates implement logic functions

- Boolean Algebra: a useful mathematical system for specifying and transforming logic functions

- We study Boolean algebra as a foundation for designing and analyzing digital systems!

# **Binary Variables**

- Recall that the two binary values have different names:

- True/False

- On/Off

- Yes/No

- 1/0

- We use 1 and 0 to denote the two values

- Variable identifier examples:

- A, B, y, z, or  $X_1$  for now

- RESET, START\_IT, or ADD1 later

# **Logical Operations**

- The three basic logical operations are:

- AND

- OR

- NOT

- AND is denoted by a dot  $(\cdot)$  or  $(\Lambda)$

- OR is denoted by a plus (+) or (V)

- NOT is denoted by an over-bar ( ), a single quote mark () after, or (~) before the variable

## **Notation Examples**

- Examples:

- $Z = X \cdot Y = XY = X \wedge Y$ : is read "Z is equal to X AND Y"

- Z = 1 if and only if X = 1 and Y = 1; otherwise, Z = 0

- $Z = X + Y = X \lor Y$ : is read "Z is equal to X OR Y"

- Z = 1 if (only X = 1) or if (only Y = 1) or if (X = 1 and Y = 1)

- $Z = \overline{X} = X' = \sim X$ : is read "Z is equal to NOT X"

• Z = 1 if X = 0; otherwise, Z = 0

- Notice the difference between arithmetic addition and logical OR:

- The statement:

1 + 1 = 2 (read "one <u>plus</u> one equals two")

is not the same as

1 + 1 = 1 (read "1 <u>or</u> 1 equals 1")

## **Operator Definitions**

Operations are defined on the values "0" and "1" for each operator:

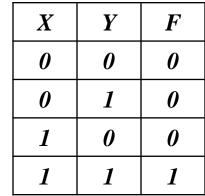

## **Truth Tables**

- *Truth table* a tabular listing of the values of a function for all possible combinations of values on its arguments

- Example: Truth tables for the basic logic operations:

| AND |      |                                            |  |        | OR | NOT       |   |                    |  |        |        |        |

|-----|------|--------------------------------------------|--|--------|----|-----------|---|--------------------|--|--------|--------|--------|

| Inp | puts | Output                                     |  | Inputs |    | Inputs    |   | Inputs             |  | Output | Inputs | Output |

| X   | Y    | $\mathbf{Z} = \mathbf{X} \cdot \mathbf{Y}$ |  | X      | Y  | Z = X + Y | X | $Z = \overline{X}$ |  |        |        |        |

| 0   | 0    | 0                                          |  | 0      | 0  | 0         | 0 | 1                  |  |        |        |        |

| 0   | 1    | 0                                          |  | 0      | 1  | 1         | 1 | 0                  |  |        |        |        |

| 1   | 0    | 0                                          |  | 1      | 0  | 1         |   |                    |  |        |        |        |

| 1   | 1    | 1                                          |  | 1      | 1  | 1         |   |                    |  |        |        |        |

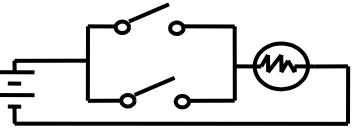

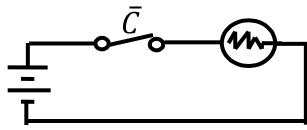

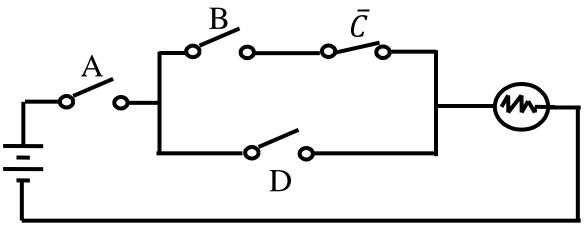

# **Logic Function Implementation**

- Using Switches

- For inputs:

- logic 1 is <u>switch closed</u>

- logic 0 is <u>switch open</u>

- For outputs:

- logic 1 is <u>light on</u>

- logic 0 is <u>light off</u>

- NOT uses a switch such that:

- logic 1 is <u>switch open</u>

- logic 0 is <u>switch closed</u>

Switches in parallel => OR

Switches in series => AND

**Normally-closed switch => NOT**

### Logic Function Implementation (Continued)

Example: Logic Using Switches

Light is

ON(L = 1) for  $L(A, B, C, D) = A \cdot (B\overline{C} + D) = AB\overline{C} + AD$ and OFF(L = 0), otherwise.

Useful model for relay circuits and for CMOS gate circuits, the foundation of current digital logic technology

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 2 - Part 1 12

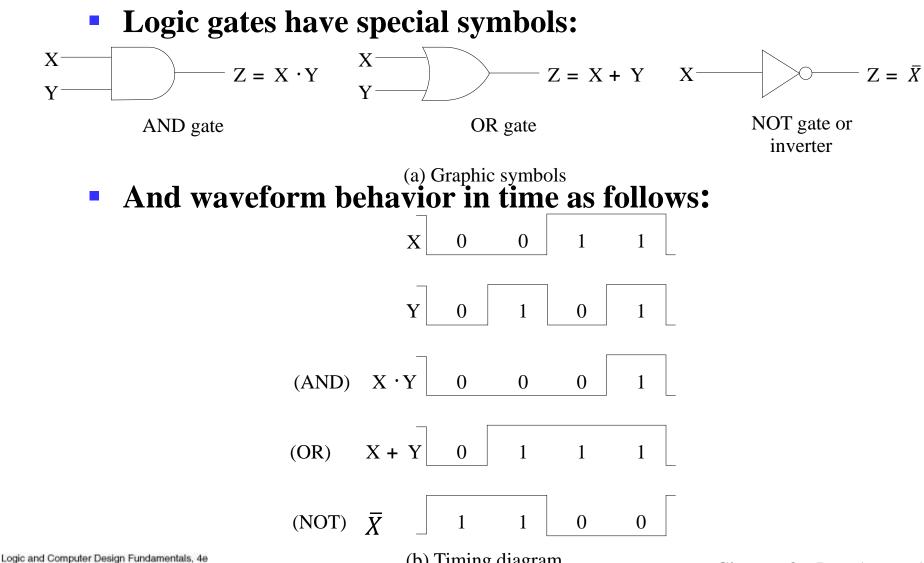

# **Logic Gates**

- In the earliest computers, switches were opened and closed by magnetic fields produced by energizing coils in *relays*. The switches in turn opened and closed the current paths

- Later, *vacuum tubes* that open and close current paths electronically replaced relays

- Today, *transistors* are used as electronic switches that open and close current paths

- Optional: Chapter 6 Part 1: The Design Space

## **Logic Gate Symbols and Behavior**

PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc. (b) Timing diagram

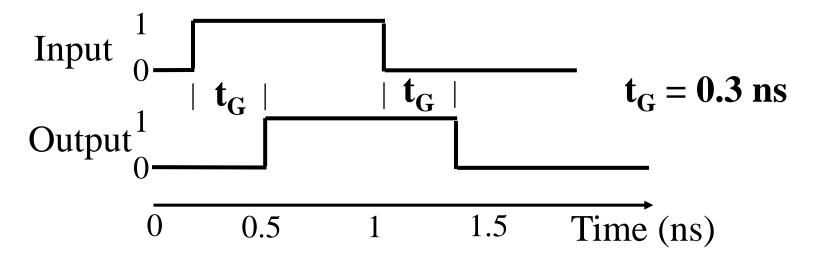

# **Gate Delay**

- In actual physical gates, if one or more input changes causes the output to change, the output change does not occur instantaneously

- The delay between an input change(s) and the resulting output change is the *gate delay* denoted by  $t_{G}$ :

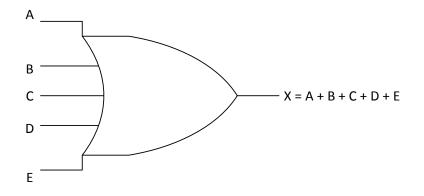

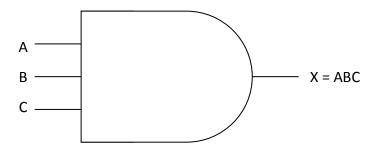

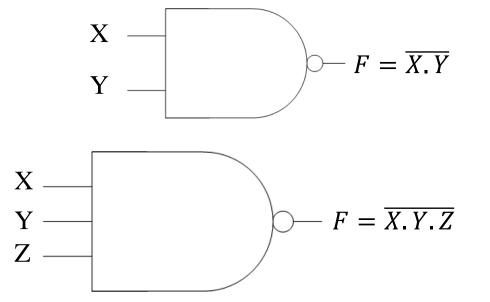

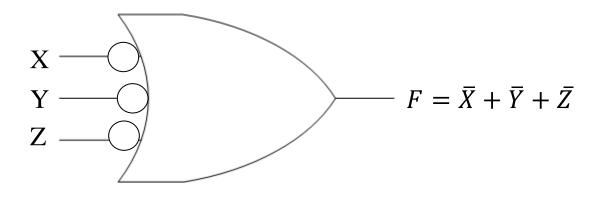

# Logic Gates: Inputs and Outputs

- NOT (inverter)

- Always one input and one output

- AND and OR gates

- Always one output

- Two or more inputs

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

# **Boolean Algebra**

- An algebra dealing with binary variables and logic operations

- Variables are designated by letters of the alphabet

- Basic logic operations: AND, OR, and NOT

- *A Boolean expression* is an algebraic expression formed by using binary variables, constants 0 and 1, the logic operation symbols, and parentheses

• E.g.: X . 1, A + B + C, (A + B)(C + D)

- *A Boolean function* consists of a binary variable identifying the function followed by equals sign and a Boolean expression

- E.g.: F = A + B + C,  $L(D, X, A) = DX + \overline{A}$

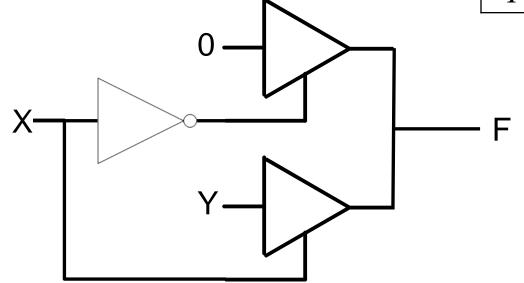

## **Logic Diagrams and Expressions**

- 1. Equation:  $F = X + \overline{Y}Z$

- 2. Logic Diagram:

- 3. Truth Table:

- Boolean equations, truth tables and logic diagrams describe the <u>same</u> function!

- Truth tables are <u>unique</u>; expressions and logic diagrams are not. This gives flexibility in implementing functions.

| X | Y | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

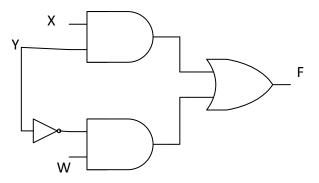

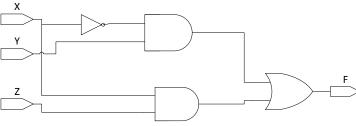

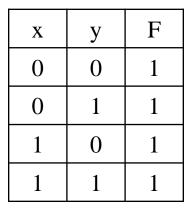

## Example

- Draw the logic diagram and the truth table of the following Boolean function:  $F(W, X, Y) = XY + W\overline{Y}$

- Logic Diagram:

- Truth Table:

| W | X | Y | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

#### This example represents a *Single Output Function*

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

## Example

- Draw the logic diagram and the truth table of the following Boolean functions:  $F(W, X) = \overline{W}\overline{X} + W, G(W, X) = W + \overline{X}$

- Logic Diagram: W Truth Table: Х W Х F G 0 0 1 1 G 0 1 0 0 1 0 1 1 1 1 1 1

This example represents a *Multiple Output Function*

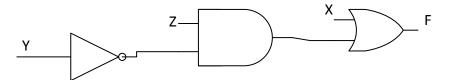

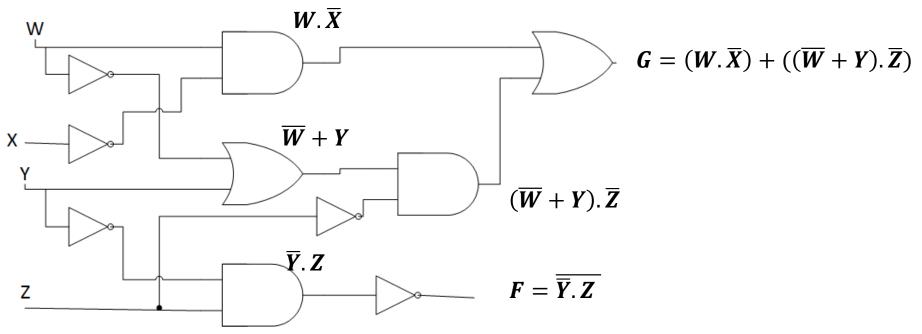

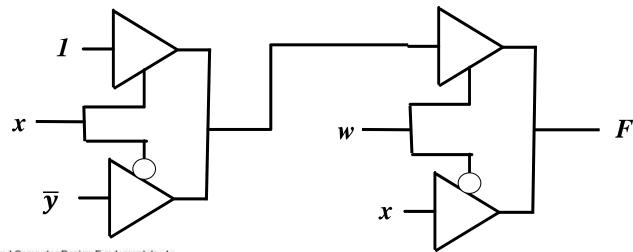

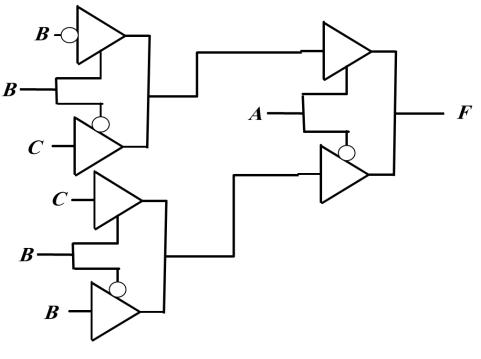

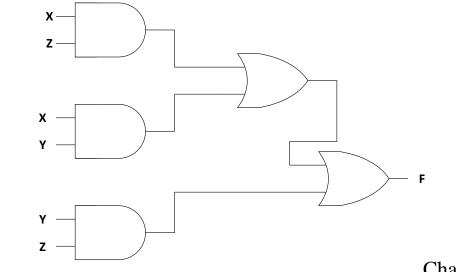

#### Example:

Given the following logic diagram, write the corresponding Boolean equation:

Logic circuits of this type are called combinational logic circuits since the variables are combined by logical operations

#### **Basic Identities of Boolean Algebra**

| <b>6</b>                                        |                                                   |                         |  |

|-------------------------------------------------|---------------------------------------------------|-------------------------|--|

| 1. $X + 0 = X$                                  | 2. $X \cdot 1 = X$                                | Evistance of 0 and 1    |  |

| 3. $X + 1 = 1$                                  | 4. $X \cdot 0 = 0$                                | Existence of 0 and 1    |  |

| 5.  X + X = X                                   | $6.  X \cdot X = X$                               | Idempotence             |  |

| $7. X + \overline{X} = 1$                       | $8. X . \overline{X} = 0$                         | Existence of complement |  |

| 9. $\overline{X} = X$                           |                                                   | Involution              |  |

| 10.X + Y = Y + X                                | 11.XY = YX                                        | Commutative Laws        |  |

| 12.(X + Y) + Z = X + (Y + Z)                    | 13.(XY)Z = X(YZ)                                  | Associative Laws        |  |

| 14.X(Y+Z) = XY + XZ                             | 15.X + YZ = (X + Y)(X + Z)                        | Distributive Laws       |  |

| $16.\overline{X+Y} = \overline{X}.\overline{Y}$ | $17.\overline{X.Y} = \overline{X} + \overline{Y}$ | DeMorgan's Laws         |  |

|                                                 |                                                   |                         |  |

#### Some Properties of Identities & the Algebra

- If the meaning is unambiguous, we leave out the symbol ....

- The identities above are organized into pairs

- The *dual* of an algebraic expression is obtained by interchanging (+) and (·) and interchanging 0's and 1's

- The identities appear in *dual* pairs. When there is only one identity on a line the identity is *self-dual*, i. e., the dual expression = the original expression.

- Unless it happens to be self-dual, the dual of an expression does not equal the expression itself

- Examples:

•

$$F = (A + \overline{C}) \cdot B + 0$$

Dual

$$F = (A \cdot \overline{C}) + B \cdot 1 = A \cdot \overline{C} + B$$

•

$$G = XY + (\overline{W + Z})$$

• Dual

$$G = (X + Y)$$

.  $\overline{WZ} = (X + Y)$ .  $(\overline{W} + \overline{Z})$

- H = AB + AC + BC

- Dual H = (A + B)(A + C)(B + C) = (A + BC)(B + C)= AB + AC + BC

- Are any of these functions self-dual?

- Yes, H is self-dual

# **Boolean Operator Precedence**

- The order of evaluation in a Boolean expression is:

- 1. Parentheses

- **2.** NOT

- 3. AND

- **4**. OR

- Consequence: Parentheses appear around OR expressions

- Examples:

- $F = A(B+C)(C+\overline{D})$

- $F = \sim AB = \overline{A}B$

- F = AB + C

- F = A(B+C)

#### **Useful Boolean Theorems**

| Theorem                                    | Dual                   | Name         |  |

|--------------------------------------------|------------------------|--------------|--|

| $x.y + \bar{x}.y = y$                      | $(x+y)(\bar{x}+y) = y$ | Minimization |  |

| $x + x \cdot y = x$                        | x.(x+y) = x            | Absorption   |  |

| $x + \bar{x} \cdot y = x + y$              | Simplification         |              |  |

| $x.y + \bar{x}.z + y.$                     | Conconcura             |              |  |

| $(x+y)(\bar{x}+z)(y+z) = (x+y)(\bar{x}+z)$ |                        | Consensus    |  |

#### **Example 1: Boolean Algebraic Proof**

•  $A + A \cdot B = A$  (Absorption Theorem)

| <b>Proof Steps</b>       | Justification (identity or theorem) |

|--------------------------|-------------------------------------|

| $A + A \cdot B$          |                                     |

| $=A \cdot 1 + A \cdot B$ | $X = X \cdot 1$                     |

| $=A \cdot (1+B)$         | Distributive Law                    |

| $=A \cdot 1$             | 1 + X = 1                           |

| =A                       | $X \cdot 1 = X$                     |

- Our primary reason for doing proofs is to learn:

- Careful and efficient use of the identities and theorems of Boolean algebra

- How to choose the appropriate identity or theorem to apply to make forward progress, irrespective of the application

#### **Example 2: Boolean Algebraic Proofs**

•  $AB + \overline{A}C + BC = AB + \overline{A}C$

(Consensus Theorem)

| <b>Proof Steps</b>                                      | Justification<br>(identity or theorem) |  |  |

|---------------------------------------------------------|----------------------------------------|--|--|

| $AB + \overline{A}C + BC$                               |                                        |  |  |

| $= AB + \overline{A}C + 1.BC$                           | <b>1</b> . $X = X$                     |  |  |

| $= AB + \overline{A}C + (A + \overline{A}).BC$          | $X + \overline{X} = 1$                 |  |  |

| $= AB + \overline{A}C + ABC + \overline{A}BC$           | Distributive Law                       |  |  |

| $= AB + ABC + \overline{A}C + \overline{A}BC$           | Commutative Law                        |  |  |

| $= AB. 1 + AB. C + \overline{A}C. 1 + \overline{A}C. B$ | X.1 = X and Commutative Law            |  |  |

| $=AB(1+C)+\overline{A}C(1+B)$                           | Distributive Law                       |  |  |

| $= AB.1 + \overline{A}C.1$                              | 1 + X = 1                              |  |  |

| $= AB + \overline{A}C$                                  | X. <b>1</b> = X                        |  |  |

# **Proof of Simplification**

•  $A + \overline{A} \cdot B = A + B$  (Simplification Theorem)

| Proof Steps              | Justification (identity or theorem) |

|--------------------------|-------------------------------------|

| $A + \overline{A}.B$     |                                     |

| $= (A + \bar{A})(A + B)$ | Distributive Law                    |

| = 1.(A + B)              | $X + \overline{X} = 1$              |

| = A + B                  | X.1 = X                             |

• A.  $(\overline{A} + B) = AB$  (Simplification Theorem)

| Proof Steps             | Justification (identity or theorem) |

|-------------------------|-------------------------------------|

| $A.(\bar{A}+B)$         |                                     |

| $= (A.\bar{A}) + (A.B)$ | Distributive Law                    |

| = 0 + AB                | $X.\overline{X} = 0$                |

| = AB                    | X + 0 = X                           |

## **Proof of Minimization**

•  $A \cdot B + \overline{A} \cdot B = B$  (Minimization Theorem)

| Proof Steps             | Justification (identity or theorem) |

|-------------------------|-------------------------------------|

| $A.B + \overline{A}.B$  |                                     |

| $= B(A + \overline{A})$ | Distributive Law                    |

| = B.1                   | $X + \overline{X} = 1$              |

| = B                     | X.1 = X                             |

#### • $(A + B)(\overline{A} + B) = B$ (Minimization Theorem)

| Proof Steps              | Justification (identity or theorem) |

|--------------------------|-------------------------------------|

| $(A+B)(\bar{A}+B)$       |                                     |

| $= B + (A.\overline{A})$ | Distributive Law                    |

| = B + 0                  | $X.\overline{X} = 0$                |

| = B                      | X + 0 = X                           |

# **Proof of DeMorgan's Laws (1)**

- $\overline{X+Y} = \overline{X} \cdot \overline{Y}$  (DeMorgan's Law)

- We will show that,  $\overline{X}$ .  $\overline{Y}$ , satisfies the definition of the complement of (X + Y), defined as  $\overline{X + Y}$  by DeMorgan's Law.

- To show this, we need to show that A + A' = 1 and  $A \cdot A' = 0$  with A = X + Y and  $A' = X' \cdot Y'$ . This proves that  $X' \cdot Y' = \overline{X + Y}$ .

- Part 1: Show X + Y + X'. Y' = 1

| Proof Steps                | Justification (identity or theorem) |  |  |

|----------------------------|-------------------------------------|--|--|

| (X+Y)+X'.Y'                |                                     |  |  |

| = (X + Y + X')(X + Y + Y') | Distributive Law                    |  |  |

| = (1+Y)(X+1)               | $X + \overline{X} = 1$              |  |  |

| = 1.1                      | X + 1 = 1                           |  |  |

| = 1                        | X.1 = X                             |  |  |

# **Proof of DeMorgan's Laws (2)**

• Part 2: Show  $(X + Y) \cdot X' \cdot Y' = 0$

| Proof Steps             | Justification (identity or theorem) |  |  |

|-------------------------|-------------------------------------|--|--|

| (X+Y). $X'$ . $Y'$      |                                     |  |  |

| = (X.X'.Y') + (Y.X'.Y') | Distributive Law                    |  |  |

| = (0.Y') + (X'.0)       | $X.\overline{X} = 0$                |  |  |

| = 0 + 0                 | X.0 = 0                             |  |  |

| = 0                     | X + 0 = X                           |  |  |

- Based on the above two parts,  $X' \cdot Y' = \overline{X + Y}$

- The second DeMorgans' law is proved by duality

- Note that DeMorgan's law, given as an identity is not an axiom in the sense that it can be proved using the other identities.

#### **Example 3: Boolean Algebraic Proofs**

•  $\overline{(X+Y)}Z + X\overline{Y} = \overline{Y}(X+Z)$

| Proof Steps                         | Justification (identity or theorem) |  |  |

|-------------------------------------|-------------------------------------|--|--|

| $\overline{(X+Y)}Z + X\overline{Y}$ |                                     |  |  |

| = X'Y'Z + X.Y'                      | DeMorgan's law                      |  |  |

| = Y'(X'Z + X)                       | Distributive law                    |  |  |

| = Y'(X + X'Z)                       | Commutative law                     |  |  |

| = Y'(X+Z)                           | Simplification Theorem              |  |  |

#### **Boolean Function Evaluation**

- $F_1 = xy\bar{z}$

- $F_2 = x + \overline{y}z$

- $F_3 = \bar{x}\bar{y}\bar{z} + \bar{x}yz + x\bar{y}$

- $F_4 = x\overline{y} + \overline{x}z$

| X | У | Z | <b>F</b> <sub>1</sub> | <b>F</b> <sub>2</sub> | F <sub>3</sub> | F <sub>4</sub> |

|---|---|---|-----------------------|-----------------------|----------------|----------------|

| 0 | 0 | 0 | 0                     | 0                     | 1              | 0              |

| 0 | 0 | 1 | 0                     | 1                     | 0              | 1              |

| 0 | 1 | 0 | 0                     | 0                     | 0              | 0              |

| 0 | 1 | 1 | 0                     | 0                     | 1              | 1              |

| 1 | 0 | 0 | 0                     | 1                     | 1              | 1              |

| 1 | 0 | 1 | 0                     | 1                     | 1              | 1              |

| 1 | 1 | 0 | 1                     | 1                     | 0              | 0              |

| 1 | 1 | 1 | 0                     | 1                     | 0              | 0              |

# **Expression Simplification**

- An application of Boolean algebra

- Simplify to contain the smallest number of <u>literals</u> (complemented and uncomplemented variables)

- Example: Simplify the following Boolean expression

- AB + A'CD + A'BD + A'CD' + ABCD

| Simplification Steps                      | Justification (identity or theorem) |

|-------------------------------------------|-------------------------------------|

| AB + A'CD + A'BD + A'CD' + ABCD           |                                     |

| = AB + ABCD + A'CD + A'CD' + A'BD         | Commutative law                     |

| = AB(1 + CD) + A'C(D + D') + A'BD         | Distributive law                    |

| = AB.1 + A'C.1 + A'BD                     | 1 + X = 1 and $X + X' = 1$          |

| = AB + A'C + A'BD                         | X.1 = X                             |

| = AB + A'BD + A'C                         | Commutative law                     |

| = B(A + A'D) + A'C                        | Distributive law                    |

| $= B(A + D) + A'C \rightarrow 5 Literals$ | Simplification Theorem              |

# **Complementing Functions**

- Use DeMorgan's Theorem to complement a function:

- 1. Interchange AND and OR operators

- 2. Complement each constant value and literal

- Example: Complement F = x'yz' + xy'z'

$$F' = (x + y' + z)(x' + y + z)$$

• Example: Complement G = (a' + bc)d' + e

$$G' = (a(b' + c') + d).e'$$

## Example

- Simplify the following:

- F = X'YZ + X'YZ' + XZ

0

0

1

1

1

1

|                   | Simplification Steps |                        | (identity or theorem)  |

|-------------------|----------------------|------------------------|------------------------|

| X'YZ + X'YZ' + XZ |                      |                        |                        |

|                   | =                    | X'Y(Z+Z')+XZ           | Distributive law       |

|                   | =                    | X'Y.1 + XZ             | X + X' = 1             |

|                   | =                    | X'Y + XZ               | X.1 = X                |

| У                 | Ζ                    | X'YZ + X'YZ' + XZ      | X'Y + XZ               |

| 0                 | 0                    | 0                      | 0                      |

| 0                 | 1                    | 0                      | 0                      |

| 1                 | 0                    | 1                      | 1                      |

| 1                 | 1                    | 1                      | 1                      |

| 0                 | 0                    | 0                      | 0                      |

| 0                 | 1                    | 1                      | 1                      |

| 1                 | 0                    | 0                      | 0                      |

| 1                 | 1                    | 1                      | 1                      |

| <br>              |                      | 3 terms and 8 literals | 2 terms and 4 literals |

#### Example

- Show that F = x'y' + xy' + x'y + xy = 1

- Solution1: Truth Table

• Solution2: Boolean Algebra

| Proof Steps           | (identity or theorem) |

|-----------------------|-----------------------|

| x'y' + xy' + x'y + xy |                       |

| = y'(x'+x) + y(x'+x)  | Distributive law      |

| = y'.1 + y.1          | X + X' = 1            |

| = y' + y              | X.1 = X               |

| = 1                   | X + X' = 1            |

#### Examples

• Show that ABC + A'C' + AC' = AB + C' using Boolean algebra.

| Proof Steps         | (identity or theorem) |

|---------------------|-----------------------|

| ABC + A'C' + AC'    |                       |

| = ABC + C'(A' + A)  | Distributive law      |

| = ABC + C'.1        | X + X' = 1            |

| = ABC + C'          | X.1 = X               |

| = (AB + C')(C + C') | Distributive law      |

| = (AB + C').1       | X + X' = 1            |

| = AB + C'           | X.1 = X               |

• Find the dual and the complement of  $f = wx + y'z \cdot 0 + w'z$

•

$$Dual(f) = (w + x)(y' + z + 1)(w' + z)$$

•

$$f' = (w' + x')(y + z' + 1)(w + z')$$

## **Overview – Canonical Forms**

- What are Canonical Forms?

- Minterms and Maxterms

- Index Representation of Minterms and Maxterms

- Sum-of-Minterm (SOM) Representations

- Product-of-Maxterm (POM) Representations

- Representation of Complements of Functions

- Conversions between Representations

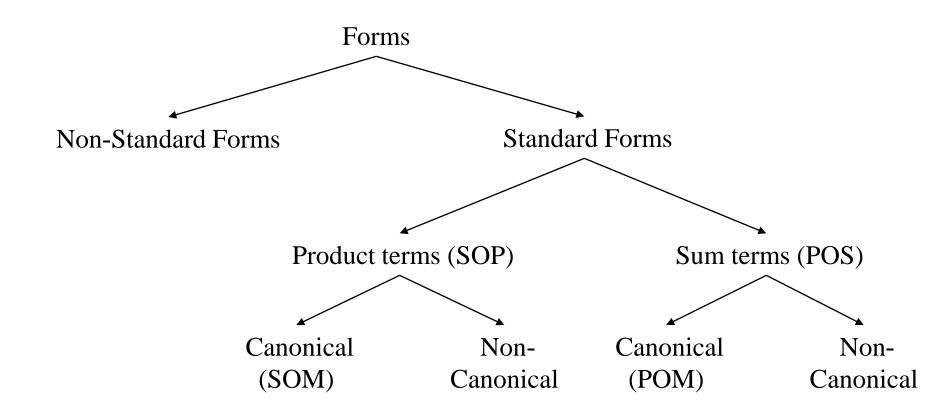

#### **Boolean Representation Forms**

# **Canonical Forms**

- It is useful to specify Boolean functions in a form that:

- Allows comparison for equality

- Has a correspondence to the truth tables

- Facilitates simplification

- Canonical Forms in common usage:

- Sum of Minterms (SOM)

- Product of Maxterms (POM)

#### Minterms

- *Minterms* are AND terms with *every variable* present in either true or complemented form

- Given that each binary variable may appear normal (e.g., x) or complemented (e.g., x̄), there are 2<sup>n</sup> minterms for n variables

- <u>Example</u>: Two variables (X and Y) produce  $2^2 = 4$  combinations:

- *XY* (both normal)

- $X\overline{Y}$  (X normal, Y complemented)

- $\overline{X}Y$  (X complemented, Y normal)

- $\overline{X}\overline{Y}$  (both complemented)

#### • Thus there are *four minterms* of two variables

#### Maxterms

- Maxterms are OR terms with every variable in true or complemented form

- Given that each binary variable may appear normal (e.g., x) or complemented (e.g., x̄), there are 2<sup>n</sup> maxterms for *n* variables

- Example: Two variables (X and Y) produce 2<sup>2</sup> = 4 combinations:

- X + Y (both normal)

- $X + \overline{Y}$  (X normal, Y complemented)

- $\overline{X} + Y$  (X complemented, Y normal)

(both complemented)

$\overline{X} + \overline{Y}$

## **Maxterms and Minterms**

• Examples: Three variable (X, Y, Z) minterms and maxterms

| Index | Minterm (m)                            | Maxterm (M)                                  |

|-------|----------------------------------------|----------------------------------------------|

| 0     | $\overline{X}\overline{Y}\overline{Z}$ | X + Y + Z                                    |

| 1     | $\overline{X}\overline{Y}Z$            | $X + Y + \overline{Z}$                       |

| 2     | $\overline{X}Y\overline{Z}$            | $X + \overline{Y} + Z$                       |

| 3     | $\overline{X}YZ$                       | $X + \overline{Y} + \overline{Z}$            |

| 4     | $X\overline{Y}\overline{Z}$            | $\overline{X} + Y + Z$                       |

| 5     | $X\overline{Y}Z$                       | $\overline{X} + Y + \overline{Z}$            |

| 6     | $XY\overline{Z}$                       | $\overline{X} + \overline{Y} + Z$            |

| 7     | XYZ                                    | $\overline{X} + \overline{Y} + \overline{Z}$ |

• The *index* above is important for describing which variables in the terms are true and which are complemented

# **Standard Order**

- Minterms and maxterms are designated with a subscript

- The subscript is a number, corresponding to a binary pattern

- The bits in the pattern represent the complemented or normal state of each variable listed in a standard order

- All variables will be present in a minterm or maxterm and will be listed in the *same order (usually alphabetically)*

- Example: For variables a, b, c:

- Maxterms:  $(a + b + \overline{c}), (a + b + c)$

- Terms: (b + a + c),  $a\overline{c}b$ , and (c + b + a) are NOT in standard order.

- Minterms:  $a\overline{b}c$ , abc,  $\overline{a}\overline{b}c$

- Terms: (a + c),  $\overline{b}c$ , and  $(\overline{a} + b)$  do not contain all variables

# **Purpose of the Index**

- The *index* for the minterm or maxterm, expressed as a binary number, is used to determine whether the variable is shown in the true form or complemented form

- For Minterms:

- "0" means the variable is "Complemented"

- "1" means the variable is "Not Complemented"

- For Maxterms:

- "0" means the variable is "Not Complemented"

- "1" means the variable is "Complemented"

#### **Index Example: Three Variables**

| Index<br>(Decimal) | Index (Binary)<br>n = 3 Variables | Minterm (m)                         | Maxterm (M)                             |

|--------------------|-----------------------------------|-------------------------------------|-----------------------------------------|

| 0                  | 000                               | $m_0 = \bar{X}\bar{Y}\bar{Z}$       | $M_0 = X + Y + Z$                       |

| 1                  | 001                               | $m_1 = \bar{X}\bar{Y}Z$             | $M_1 = X + Y + \bar{Z}$                 |

| 2                  | 010                               | $m_2 = \bar{X}Y\bar{Z}$             | $M_2 = X + \overline{Y} + Z$            |

| 3                  | 011                               | $m_3 = \overline{X}YZ$              | $M_3 = X + \overline{Y} + \overline{Z}$ |

| 4                  | 100                               | $m_4 = X \overline{Y} \overline{Z}$ | $M_4 = \bar{X} + Y + Z$                 |

| 5                  | 101                               | $m_5 = X\overline{Y}Z$              | $M_5 = \bar{X} + Y + \bar{Z}$           |

| 6                  | 110                               | $m_6 = XY\overline{Z}$              | $M_6 = \overline{X} + \overline{Y} + Z$ |

| 7                  | 111                               | $m_7 = XYZ$                         | $M_7 = \bar{X} + \bar{Y} + \bar{Z}$     |

## **Index Example: Four Variables**

| i (Decimal) | i (Binary)<br>n = 4 Variables | m <sub>i</sub>                          | $\mathbf{M}_{\mathbf{i}}$                        |

|-------------|-------------------------------|-----------------------------------------|--------------------------------------------------|

| 0           | 0000                          | $ar{a}ar{b}ar{c}ar{d}$                  | a+b+c+d                                          |

| 1           | 0001                          | $\overline{a}\overline{b}\overline{c}d$ | $a + b + c + \overline{d}$                       |

| 3           | 0011                          | $\overline{a}\overline{b}cd$            | $a + b + \bar{c} + \bar{d}$                      |

| 5           | 0101                          | $ar{a}bar{c}d$                          | $a + \overline{b} + c + \overline{d}$            |

| 7           | 0111                          | $ar{a}bcd$                              | $a + \overline{b} + \overline{c} + \overline{d}$ |

| 10          | 1010                          | $a\overline{b}c\overline{d}$            | $\bar{a} + b + \bar{c} + d$                      |

| 13          | 1101                          | abīcd                                   | $\bar{a} + \bar{b} + c + \bar{d}$                |

| 15          | 1111                          | abcd                                    | $\bar{a} + \bar{b} + \bar{c} + \bar{d}$          |

#### **Minterm and Maxterm Relationship**

- Review: DeMorgan's Theorem

- $\overline{x.y} = \overline{x} + \overline{y}$  and  $\overline{x+y} = \overline{x}.\overline{y}$

- Two-variable example:

- $M_2 = \overline{x} + y$  and  $m_2 = x \cdot \overline{y}$

- Using DeMorgan's Theorem  $\rightarrow \overline{x} + y = \overline{x} \cdot \overline{y} = x \cdot \overline{y}$

- Using DeMorgan's Theorem  $\rightarrow \overline{x. \overline{y}} = \overline{x} + \overline{\overline{y}} = \overline{x}. y$

- Thus, M<sub>2</sub> is the complement of m<sub>2</sub> and vice-versa

- Since DeMorgan's Theorem holds for *n* variables, the above holds for terms of *n* variables:

$$M_i = \overline{m_i}$$

and  $m_i = \overline{M_i}$

• Thus, M<sub>i</sub> is the complement of m<sub>i</sub> and vice-versa

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 2 - Part 1 50

## **Function Tables for Both**

Minterms of 2 variables:

Maxterms of 2 variables:

| xy | m <sub>0</sub> | <b>m</b> <sub>1</sub> | <b>m</b> <sub>2</sub> | m <sub>3</sub> |

|----|----------------|-----------------------|-----------------------|----------------|

| 00 | 1              | 0                     | 0                     | 0              |

| 01 | 0              | 1                     | 0                     | 0              |

| 10 | 0              | 0                     | 1                     | 0              |

| 11 | 0              | 0                     | 0                     | 1              |

| xy | M <sub>0</sub> | M <sub>1</sub> | <b>M</b> <sub>2</sub> | <b>M</b> <sub>3</sub> |

|----|----------------|----------------|-----------------------|-----------------------|

| 00 | 0              | 1              | 1                     | 1                     |

| 01 | 1              | 0              | 1                     | 1                     |

| 10 | 1              | 1              | 0                     | 1                     |

| 11 | 1              | 1              | 1                     | 0                     |

Each column in the maxterm function table is the complement of the column in the minterm function table since M<sub>i</sub> is the complement of m<sub>i</sub>.

## **Observations**

- In the function tables:

- Each *minterm* has one and only one 1 present in the  $2^n$  terms (a <u>minimum</u> of 1s). All other entries are 0.

- Each *maxterm* has one and only one 0 present in the 2<sup>*n*</sup> terms All other entries are 1 (a <u>maximum</u> of 1s).

- We can implement any function by

- "ORing" the minterms corresponding to "1" entries in the function table. These are called the minterms of the function.

- "ANDing" the maxterms corresponding to "0" entries in the function table. These are called the maxterms of the function.

- This gives us two <u>canonical forms</u> for stating any Boolean function:

- Sum of Minterms (SOM)

- Product of Maxterms (POM)

#### **Minterm Function Example**

• Example: Find  $F_1 = m_1 + m_4 + m_7$

•

$$F_1 = x'y'z + xy'z' + xyz$$

| xyz | Index | $m_1 + m_4 + m_7 = F_1$ |

|-----|-------|-------------------------|

| 000 | 0     | 0 + 0 + 0 = 0           |

| 001 | 1     | 1 + 0 + 0 = 1           |

| 010 | 2     | 0 + 0 + 0 = 0           |

| 011 | 3     | 0 + 0 + 0 = 0           |

| 100 | 4     | 0 + 1 + 0 = 1           |

| 101 | 5     | 0 + 0 + 0 = 0           |

| 110 | 6     | 0 + 0 + 0 = 0           |

| 111 | 7     | 0 + 0 + 1 = 1           |

## **Minterm Function Example**

- $F(A, B, C, D, E) = m_2 + m_9 + m_{17} + m_{23}$

- F(A, B, C, D, E) = A'B'C'DE' + A'BC'D'E+ AB'C'D'E + AB'CDE

## **Maxterm Function Example**

- Example: Implement F1 in maxterms:

- $F_1 = M_0 \cdot M_2 \cdot M_3 \cdot M_5 \cdot M_6$

- $F_1 = (x + y + z) \cdot (x + y' + z) \cdot (x + y' + z') \cdot (x' + y + z') \cdot (x' + y' + z)$

| xyz | Index | $M_0 . M_2 . M_3 . M_5 . M_6 = F_1$     |

|-----|-------|-----------------------------------------|

| 000 | 0     | 0.1.1.1.1 = 0                           |

| 001 | 1     | $1 \cdot 1 \cdot 1 \cdot 1 = 1$         |

| 010 | 2     | $1 \cdot 0 \cdot 1 \cdot 1 \cdot 1 = 0$ |

| 011 | 3     | $1 \cdot 1 \cdot 0 \cdot 1 \cdot 1 = 0$ |

| 100 | 4     | $1 \cdot 1 \cdot 1 \cdot 1 = 1$         |

| 101 | 5     | $1 \cdot 1 \cdot 1 \cdot 0 \cdot 1 = 0$ |

| 110 | 6     | $1 \cdot 1 \cdot 1 \cdot 1 \cdot 0 = 0$ |

| 111 | 7     | $1 \cdot 1 \cdot 1 \cdot 1 = 1$         |

## **Maxterm Function Example**

•  $F(A, B, C, D) = M_3 \cdot M_8 \cdot M_{11} \cdot M_{14}$

•

$$F(A, B, C, D)$$

=  $(A + B + C' + D') \cdot (A' + B + C + D) \cdot (A' + B + C' + D') \cdot (A' + B' + C' + D)$

# **Canonical Sum of Minterms**

- Any Boolean function can be expressed as a <u>Sum</u> <u>of Minterms (SOM)</u>:

- For the function table, the <u>minterms</u> used are the terms corresponding to the 1's

- For expressions, <u>expand</u> all terms first to explicitly list all minterms. Do this by "ANDing" any term missing a variable v with a term  $(v + \bar{v})$

- Example: Implement  $f = x + \overline{x}\overline{y}$  as a SOM?

- 1. Expand terms  $\rightarrow f = x(y + \bar{y}) + \bar{x}\bar{y}$

- 2. Distributive law  $\rightarrow f = xy + x\overline{y} + \overline{x}\overline{y}$

- 3. Express as SOM  $\rightarrow f = m_3 + m_2 + m_0 = m_0 + m_2 + m_3$

# **Another SOM Example**

• Example:

$$F = A + \overline{B}C$$

- There are three variables: A, B, and C which we take to be the standard order

- Expanding the terms with missing variables:

- $F = A(B + \overline{B})(C + \overline{C}) + (A + \overline{A})\overline{B}C$

- Distributive law:

- $F = ABC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + A\overline{B}C + \overline{A}\overline{B}C$

- Collect terms (removing all but one of duplicate terms):

- $F = ABC + AB\overline{C} + A\overline{B}C + A\overline{B}\overline{C} + \overline{A}\overline{B}C$

- Express as SOM:

•

$$F = m_7 + m_6 + m_5 + m_4 + m_1$$

•  $F = m_1 + m_4 + m_5 + m_6 + m_7$

Logic and Computer Design Fundamentals, « PowerPoint® Slides © 2008 Pearson Education, Inc.

#### **Shorthand SOM Form**

- From the previous example, we started with:

F = A + BC

- We ended up with:

- $F = m_1 + m_4 + m_5 + m_6 + m_7$

- This can be denoted in the *formal shorthand*:

- $F(A, B, C) = \sum_{m} (1, 4, 5, 6, 7)$

- Note that we explicitly show the standard variables in order and drop the "m" designators.

#### **Canonical Product of Maxterms**

- Any Boolean Function can be expressed as a <u>Product of Maxterms (POM)</u>:

- For the function table, the maxterms used are the terms corresponding to the 0's

- For an expression, expand all terms first to explicitly list all maxterms. Do this by first applying the second distributive law, "ORing" terms missing variable v with  $(v \cdot \overline{v})$  and then applying the distributive law again

- Example: Convert  $f(x, y, z) = x + \overline{x}\overline{y}$  to POM?

- Distributive law  $\rightarrow f = (x + \overline{x}) \cdot (x + \overline{y}) = x + \overline{y}$

- ORing with missing variable (z)  $\rightarrow f = x + \overline{y} + z \cdot \overline{z}$

- Distributive law  $\rightarrow f = (x + \overline{y} + z) \cdot (x + \overline{y} + \overline{z})$

- Express as POS  $\rightarrow f = M_2 \cdot M_3$

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

#### **Another POM Example**

- Convert f(A, B, C) = AC' + BC + A'B' to POM?

- Use  $x + yz = (x + y) \cdot (x + z)$ , assuming x = AC' + BC and y = A' and z = B'

- $f(A, B, C) = (AC' + BC + A') \cdot (AC' + BC + B')$

- Use Simplification theorem to get:

- $f(A, B, C) = (BC + A' + C') \cdot (AC' + B' + C)$

- Use Simplification theorem again to get:

- $f(A, B, C) = (A' + B + C') \cdot (A + B' + C) = M_5 \cdot M_2$

- $f(A, B, C) = M_2 \cdot M_5 = \prod_M (2,5) \rightarrow Shorthand POM$ form

# **Function Complements**

- The complement of a function expressed as a sum of minterms is constructed by selecting the minterms missing in the sum-of-minterms canonical forms.

- Alternatively, the complement of a function expressed by a sum of minterms form is simply the Product of Maxterms with the same indices.

- Example: Given  $F(x, y, z) = \sum_{m} (1,3,5,7)$ , find complement F as SOM and POM?

•

$$\overline{F}(x, y, z) = \sum_{m} (0, 2, 4, 6)$$

•  $\overline{F}(x, y, z) = \prod_{M} (1, 3, 5, 7)$

## **Conversion Between Forms**

- To convert between sum-of-minterms and product-of-maxterms form (or vice-versa) we follow these steps:

- Find the function complement by swapping terms in the list with terms not in the list.

- Change from products to sums, or vice versa.

- Example: Given F as before:  $F(x, y, z) = \sum_{m} (1, 3, 5, 7)$

- Form the Complement:

$\overline{F}(x, y, z) = \sum_{m} (0, 2, 4, 6)$

• Then use the other form with the same indices – this forms the complement again, giving the other form of the original function:  $E(x, y, z) = \prod_{i=1}^{n} (0.2.4.6)$

$F(x, y, z) = \prod_{M} (0, 2, 4, 6)$

# Important Properties of Minterms

- Maxterms are seldom used directly to express Boolean functions

- Minterms properties:

- For *n* Boolean variables, there are  $2^n$  minterms (0 to  $2^n$  -1)

- Any Boolean function can be represented as a logical sum of minterms (SOM)

- The complement of a function contains those minterms not included in the original function

- A function that include all the 2<sup>n</sup> minterms is equal to 1

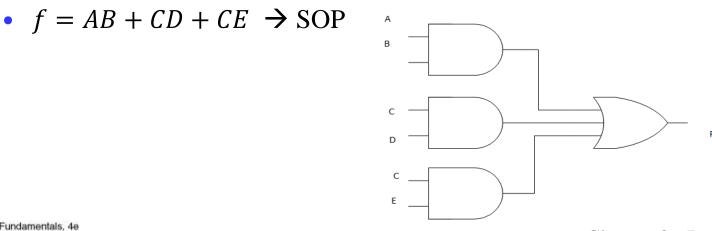

#### **Standard Forms**

- Standard Sum-of-Products (SOP) form: equations are written as an OR of AND terms

- <u>Standard Product-of-Sums (POS) form:</u> equations are written as an AND of OR terms

- Examples:

- SOP:  $ABC + \overline{A}\overline{B}C + B$

- POS:  $(A + B) \cdot (A + \overline{B} + \overline{C}) \cdot C$

- These "mixed" forms are <u>neither SOP nor POS</u>

- (AB+C)(A+C)

- $AB\overline{C} + AC(A+B)$

# **Standard Sum-of-Products (SOP)**

- A sum of minterms form for *n* variables can be written down directly from a truth table

- Implementation of this form is a two-level network of gates such that:

- The first level consists of *n*-input AND gates, and

- The second level is a single OR gate (with fewer than 2<sup>n</sup> inputs)

- This form often can be simplified so that the corresponding circuit is simpler

# **Standard Sum-of-Products (SOP)**

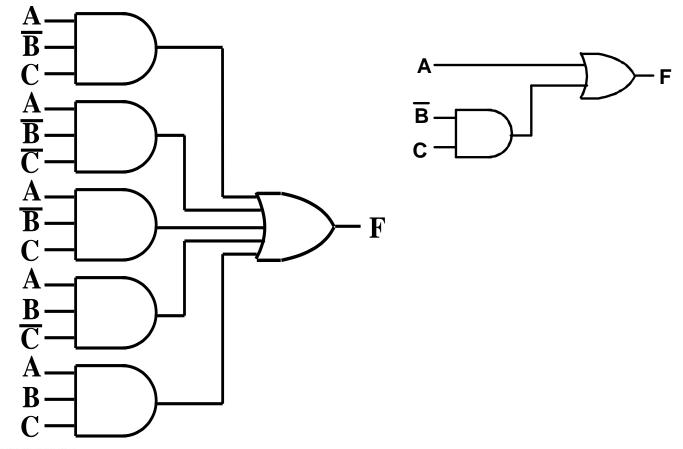

- A Simplification Example:  $F(A, B, C) = \sum_{m} (1, 4, 5, 6, 7)$

- Writing the minterm expression:

- F(A, B, C) = A'B'C + AB'C' + AB'C + ABC' + ABC

- Simplifying using boolean Algebra:

| Simplification Steps               | (identity or theorem)  |  |

|------------------------------------|------------------------|--|

| A'B'C + AB'C' + AB'C + ABC' + ABC  |                        |  |

| = A'B'C + AB'(C' + C) + AB(C' + C) | Distributive law       |  |

| = A'B'C + AB' + AB                 | X + X' = 1             |  |

| = A'B'C + A(B' + B)                | Distributive law       |  |

| = A'B'C + A                        | Simplification Theorem |  |

| = A + B'C                          |                        |  |

Simplified F contains 3 literals compared to 15 in minterm F

#### **AND/OR Two-level Implementation** of SOP Expression

The two implementations for F are shown below – it is quite apparent which is simpler!

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Two-level Implementation**

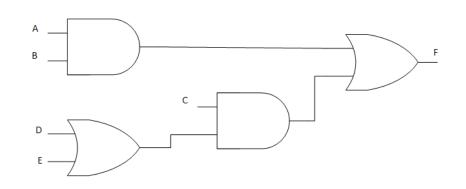

Draw the logic diagram of the following boolean function:

•

$$f = AB + C(D + E)$$

Represent the function using two-level implementation:

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

# **SOP and POS Observations**

- The previous examples show that:

- Canonical Forms (Sum-of-minterms, Product-of-Maxterms), or other standard forms (SOP, POS) differ in complexity

- Boolean algebra can be used to manipulate equations into simpler forms.

- Simpler equations lead to simpler two-level implementations

- Questions:

- How can we attain a "simplest" expression?

- Is there only one minimum cost circuit?

- The next part will deal with these issues.

# Logic and Computer Design Fundamentals Chapter 2 – Combinational Logic Circuits

Part 2 – Circuit Optimization

**Charles Kime & Thomas Kaminski**

© 2008 Pearson Education, Inc. (Hyperlinks are active in View Show mode)

Updated by Dr. Waleed Dweik

#### Overview

#### Part 1 – Gate Circuits and Boolean Equations

- Binary Logic and Gates

- Boolean Algebra

- Standard Forms

- Part 2 Circuit Optimization

- Two-Level Optimization

- Map Manipulation

- Part 3 Additional Gates and Circuits

- Other Gate Types

- Exclusive-OR Operator and Gates

- High-Impedance Outputs

# **Circuit Optimization**

- Goal: To obtain the simplest implementation for a given function

- Optimization is a more formal approach to simplification that is performed using a specific procedure or algorithm

- Optimization requires a cost criterion to measure the simplicity of a circuit

- Distinct cost criteria we will use:

- Literal cost (L)

- Gate input cost (G)

- Gate input cost with NOTs (GN)

#### **Literal Cost**

- *Literal:* a variable or its complement

- Literal cost (L): the number of literal appearances in a Boolean expression corresponding to the logic circuit diagram

- Examples:

- F = BD + AB'C + AC'D'

- L = 8 (Minimum cost  $\rightarrow$  Best solution)

- F = BD + AB'C + AB'D' + ABC'

- *L* = 11

- F = (A + B)(A + D)(B + C + D')(B' + C' + D)• L = 10

# **Gate Input Cost**

- *Gate input cost (G):* the number of inputs to the gates in the implementation corresponding exactly to the given equation or equations. (*G: inverters not counted, GN: inverters counted*)

- For SOP and POS equations, it can be found from the equation(s) by finding the sum of:

- All literal appearances

- The number of terms excluding single literal terms,(G) and

- optionally, the number of distinct complemented single literals (GN).

- Examples:

- F = BD + AB'C + AC'D'

- G = 11, GN = 14 (Minimum cost  $\rightarrow$  Best solution)

- F = BD + AB'C + AB'D' + ABC'

- *G* = 15, *GN* = 18

•

$$F = (A + B)(A + D)(B + C + D')(B' + C' + D)$$

•  $G = 14, GN = 17$

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

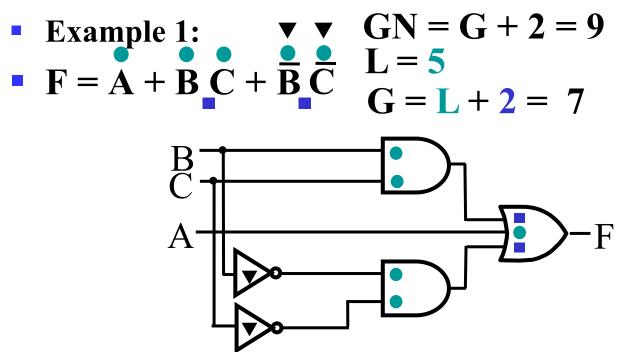

#### **Cost Criteria** (continued)

- L (literal count) counts the AND inputs and the single literal OR input.

- G (gate input count) adds the remaining OR gate inputs

- GN(gate input count with NOTs) adds the inverter inputs

#### Cost Criteria (continued)

Example 2:

•

$$F = (A, B, C, D) = (ABC + D').C'$$

- *L* = 5

- G = 5 + 2 = 7

- GN = 7 + 2 = 9

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

# **Cost Criteria** (continued)

- Example 3:

- $\mathbf{F} = \mathbf{A} \mathbf{B} \mathbf{C} + \mathbf{\overline{A}} \mathbf{\overline{B}} \mathbf{\overline{C}}$

- L = 6, G = 8, GN = 11

- $\mathbf{F} = (\mathbf{A} + \mathbf{\overline{C}})(\mathbf{\overline{B}} + \mathbf{C})(\mathbf{\overline{A}} + \mathbf{B})$

•

$$L = 6$$

,  $G = 9$ ,  $GN = 12$

- <u>Same</u> function and <u>same</u> literal cost

- But first circuit has <u>better</u> gate input count and <u>better</u> gate input count with NOTs

- Select it!

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

# **Boolean Function Optimization**

- Minimizing the gate input (or literal) cost of a (a set of) Boolean equation(s) reduces circuit cost

- We choose gate input cost

- Boolean Algebra and graphical techniques are tools to minimize cost criteria values

- Some important questions:

- When do we stop trying to reduce the cost?

- Do we know when we have a minimum cost?

- Treat optimum or near-optimum cost functions for two-level (SOP and POS) circuits

- Introduce a graphical technique using Karnaugh maps (K-maps, for short)

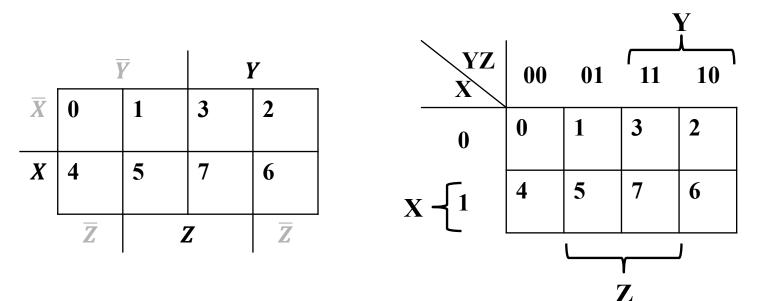

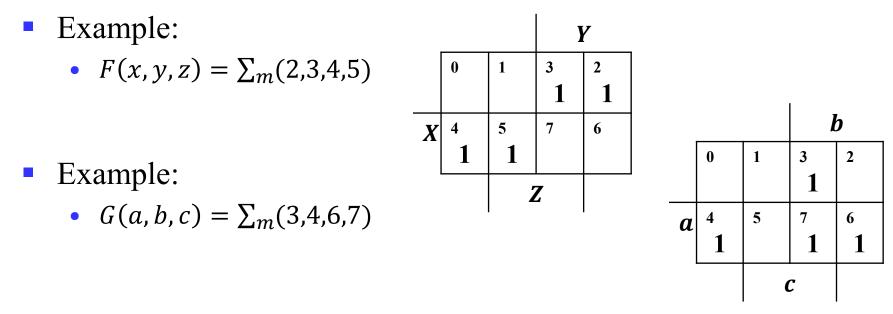

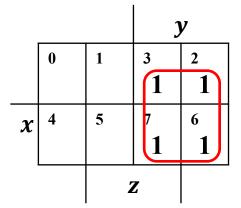

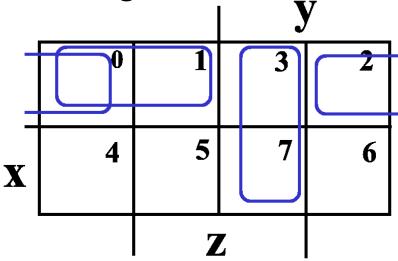

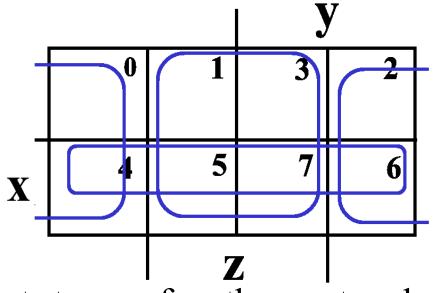

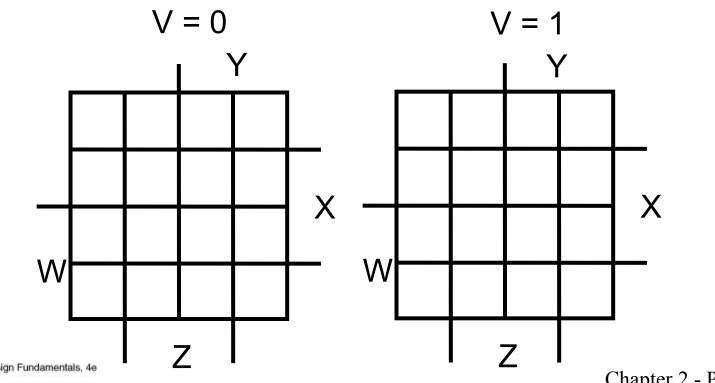

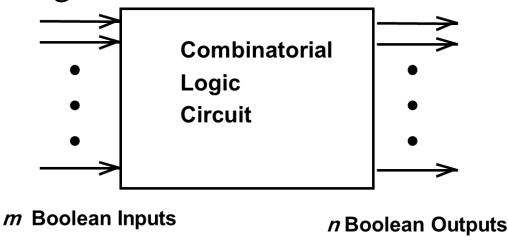

# Karnaugh Maps (K-map)

- A K-map is a collection of squares

- Graphical representation of the truth table

- Each square represents a minterm, or a maxterm, or a row in the truth table

- For n-variable, there are 2<sup>n</sup> squares

- The collection of squares is a graphical representation of a Boolean function

- Adjacent squares differ in the value of one variable

- Alternative algebraic expressions for the same function are derived by recognizing patterns of squares

# Some Uses of K-Maps

- Finding optimum or near optimum

- SOP and POS standard forms, and

- two-level AND/OR and OR/AND circuit implementations

for functions with small numbers of variables

- Visualizing concepts related to manipulating Boolean expressions, and

- Demonstrating concepts used by computeraided design programs to simplify large circuits

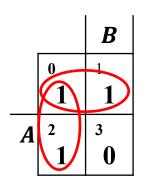

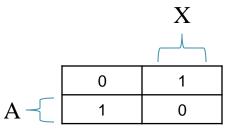

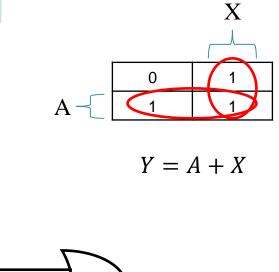

#### **Two Variable Maps**

- A 2-variable Karnaugh Map:

- Note that minterm  $m_0$  and y = 0 y = 1minterm  $m_1$  are "adjacent" x = 0  $m_0 = \overline{x}\overline{y}$   $m_1 = \overline{x}y$ and differ in the value of the x = 1  $m_2 = x\overline{y}$   $m_3 = xy$ variable y

- Similarly, minterm m<sub>0</sub> and minterm m<sub>2</sub> differ in the x variable

- Also, m<sub>1</sub> and m<sub>3</sub> differ in the x variable as well

- Finally, m<sub>2</sub> and m<sub>3</sub> differ in the value of the variable y