10

smi)e tor life

$r=12 \rightarrow not common$   $0,1,2,\ldots,a,b$

= 64 k

|                      |                                                                                                        | مه عشي و لياق الأغمة.                                  |

|----------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|                      | No                                                                                                     |                                                        |

|                      | (46,6875/10)=<br>iAleger                                                                               |                                                        |

|                      | Convert Integer                                                                                        | 180                                                    |

| الازگاران            | 46÷2 23<br>23÷2 11                                                                                     | R [ 50 ] [ 5 ] [ 5 ] [ 5] [ 5] [ 5] [ 5]               |

|                      | 11 ÷ 2 5<br>5 ÷ 2 2<br>2 ÷ 2 1                                                                         | 1 2000                                                 |

|                      | 1 ÷ 2                                                                                                  | I M3D                                                  |

| الأرقا) (            | $(46)_{10} = (161110)_{2}$<br>$3.6875 \times 2$<br>$3.75 \times 2$<br>$3.5 \times 2$<br>$3.5 \times 2$ | 2 1.3 75  (0. 75  1.5  1.5  1.5  1.5  1.5  1.5  1.5  1 |

| 7                    | (0.6275) = ((                                                                                          |                                                        |

| آنر التي<br>بدن معنه | (101110.1011)2                                                                                         |                                                        |

No. = (231.406) 8 × (153.513)10  $R \rightarrow (0 \rightarrow 7)$ (1)153/8 Truncate. LSD 19 19/8 2 MZD 2/8 2 M 3D 2 0.513x 8 O 41.104 No round 0.104 X8 8 35 O. 835 X 3 6), 65 6 130 4 5 Round 0.656X8 5. Ţ 6.46 75 -0-4375 6.410 0.440  $\times (423)_{10} = (1A7)_{16}$ R Q 423/16 13D 26 F 26/16 10 0 MSP 1/16

No. 46-32 = 14 1=5 5 4 3 2 1 0 , -1 -2 -3-4 1011.0.1011 14-8 = 6 i = 3 i = 26-4 2  $\dot{c} = 1$ 2 - 2 0.6875 - 0.5 = 0.18750.1875 - 0.125 = 0.06250.6625 - 6.6625 = 00.25 0.125 0.0625 64 32 16 8 4 2 1. 05 0 (108.25) 1 . 0.5 0.25 00.0. 512 64 4

$$\times = 2^{\circ}$$

\* Octal to binary hexa to binarg

$\times (673.12)_{8} = (110 111 011 .001 010)_{2}$   $\times (346.0)_{6} = (0011 1010 0110 .1100)$

( Point ) ine no Isie (c) &

×(635.177)

00010 611 101, - 601 111 11/000

$\frac{(365)_{r} = (194)_{10}}{3r^{2} + 6r' + 5 \times r^{0} = 194}$   $3r^{2} + 6r + 5 - 194 = 0$

(r-7)(r+q)=0

smi)e tor life

$$= [\log_{2} 10]$$

$$= [\log_{2} 2]$$

$$= 4$$

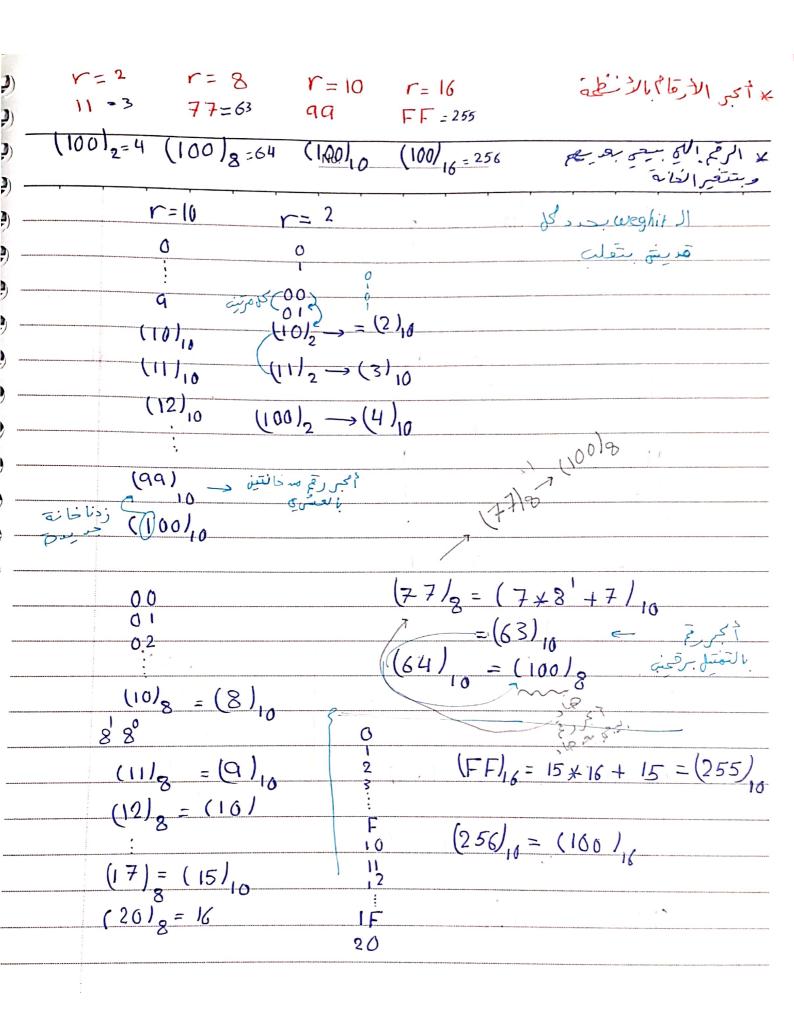

$$r^{n} \ge M > r^{n-1} \qquad 2^{q} = 512$$

$$n = [\log_{2} 365] = [\log_{2} 2^{n}] = 9$$

$$365 \rightarrow n = [\log_{2} 365] \qquad r^{n} \rightarrow 8^{3} = 512$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$n = [\log_{2} 8] = 3$$

$$r \quad \text{Maximum "M"} \rightarrow r^{n}$$

$$r \quad \text{Maximum "M"}$$

$\mathcal{Z}(X,y) = X \cdot y = X^{\prime}y = Xy$ لے حمل رفی أنه 2 معقد 2-vari de Zequals X AND y Z=1 if and only if x=-1 AND y=-1Z=0  $\overline{C} = 1$  C = 0\* CMOS transistors - ilp goeinal 56 L(A,B,C,D)=A.D+A.B.c.

2-16

Bconic resim el ais aciditel 12 3 4

No.

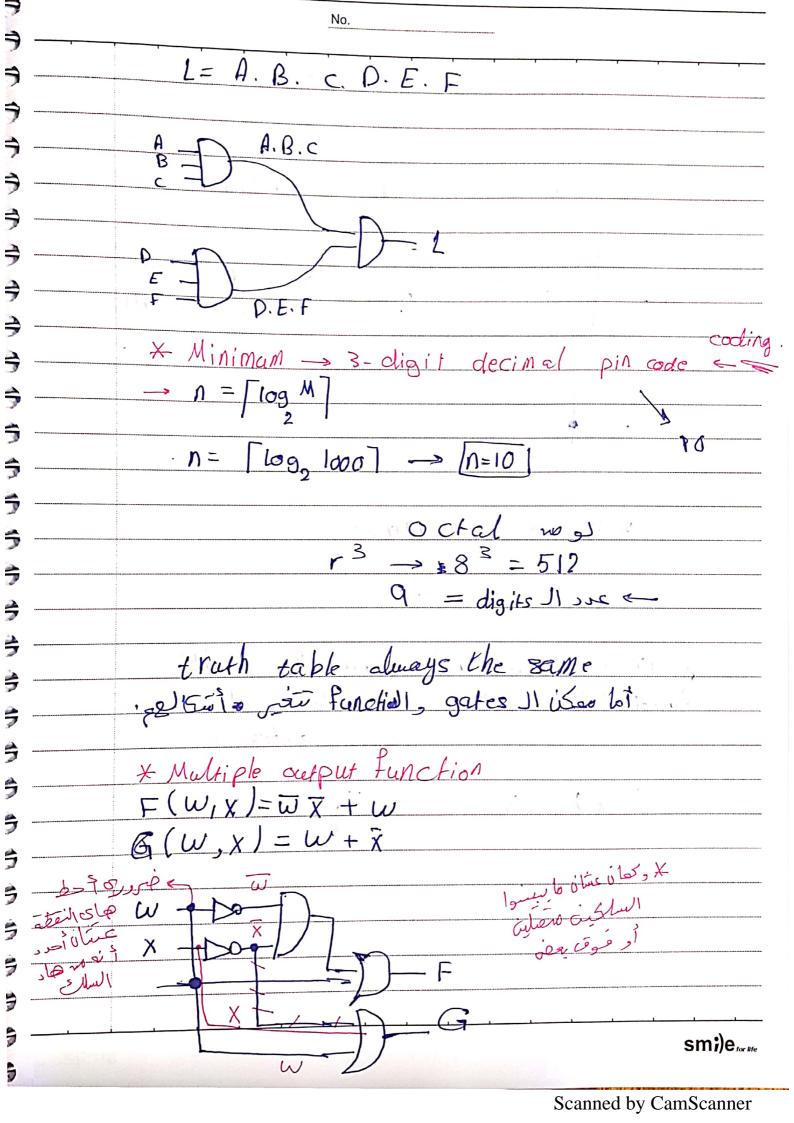

L= A. B. C. D. E. F

A.B.C

B D

P.E. F

$$(x+y) \cdot \overline{x}, \overline{g} \stackrel{?}{=} 0,$$

$$\overline{x} \cdot \overline{y} \cdot x + \overline{x} \cdot y \cdot y \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot x + \overline{x} \cdot y \cdot y \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot x + \overline{x} \cdot y \cdot y \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot x + \overline{x} \cdot y \cdot y \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot x + \overline{x} \cdot y \cdot y \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot x \cdot y \cdot \overline{y} \cdot \overline{x} + x \cdot y \cdot \overline{y} \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} + x \cdot y \cdot \overline{y} \quad A \cdot \overline{A} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} \cdot \overline{y} \cdot \overline{x} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{y} \cdot \overline{y} \cdot \overline{y} = 0$$

$$x \cdot \overline{$$

(a/+bc). d/+e

Empelose dlas X التركين على الأقوالير

(a. (b+=)+d). ē

في السؤال صوالاقواس

الأقواله الرّيادم الهيم ما بندط عليها خرةً .

- = x '97 + x '97 + x 7 (+) of of Il ils abi to 3-terms slo 55in

Literals > X Theid weren X

Osle = constant a 1 => function co' is i i too

$X = (X, g, Z) = X \cdot g \cdot Z + \overline{X} \cdot \overline{Z} (X + \overline{y})$   $= \sum_{N \in \mathbb{N}} N \circ N = \text{tandard} \qquad (9 \text{ missing})$   $= X \cdot \overline{g} \cdot \overline{Z} + \overline{X} \cdot \overline{Z} \qquad (2 \text{ AND term})$

C> sum of product = product term

product of sums (POS)

\* binary ⇒ n variables minterms = 2" = AND  $maxterms = 2^h \leftarrow \alpha R$

) + 4

smi)e,, III

|     | NO.                                                         |

|-----|-------------------------------------------------------------|

|     | $F(x,y) = \overline{x}y + xy  SOP \mid SOM$                 |

|     | $G(x, 9) = (\bar{x} + \bar{9}) \cdot (x + \bar{y})$ pos/POM |

| -   |                                                             |

|     | * m = minterns mi index                                     |

|     | $m_0 = \overline{X}\overline{y}\overline{z}$                |

|     | Minterms                                                    |

|     | $0 \rightarrow comptement$                                  |

|     | $M_{\perp} = \overline{X} \overline{y} \overline{z}$        |

|     |                                                             |

|     | $m_2 = \overline{X} \cdot \overline{Y} \cdot \overline{Z}$  |

|     | olo marken solven solven                                    |

|     | $m_3$                                                       |

|     |                                                             |

|     | * M = Maxterms Mi                                           |

|     | 11                                                          |

|     | $M_0 = X + y + 7$                                           |

|     |                                                             |

|     | $M_1 = X + 9 + \overline{2}$                                |

|     | $M_2 = X + \overline{y} + \overline{z}$                     |

| 421 |                                                             |

| 111 | Taja sec Misel Jajo le 4 00 kd pt 7                         |

| 247 |                                                             |

| 111 | 1 [15], ,, & ,,                                             |

|     |                                                             |

|     |                                                             |

Max term

complement

M13 = 0 + b + c + d

1101

\* mi = H;  $\mathcal{L}_{i} = \overline{m_{i}}$

ما يحون كل Minterms موجودته بعطينا الحوال 1

O olayl Liber is Maxterms, is Il .x

$+ F(x,y) = \overline{X}y + \overline{X}y + \overline{X}y + \overline{X}y = 1$

\* G(x, q)= (\(\bar{X} + \bar{y}\). (\(\bar{X} + \bar{q}\)), (\(\bar{X} + \bar{q}\)) (\(\bar{X} + \bar{q}\)) = 0

العلامة يسعع complement

|               |             | J                                 | Hinimum No                  | imber of or | les <                                                  |

|---------------|-------------|-----------------------------------|-----------------------------|-------------|--------------------------------------------------------|

|               |             | No.                               |                             |             | -: Minderms-!                                          |

|               | XY          | $m_o = \overline{X} \overline{Q}$ |                             |             |                                                        |

|               | 0 0         | <u> </u>                          | •                           | J           | _                                                      |

|               | 1 0         | 0                                 | 1                           | 0           | <u> </u>                                               |

|               | 1 0         | 0                                 | Ó                           |             | <u> </u>                                               |

|               | 1           | Ö                                 | 0                           | Ó           |                                                        |

|               | × F (       | x,9)= x 5                         | + X q                       |             |                                                        |

|               |             |                                   | + m 2                       |             |                                                        |

|               | _           |                                   | Λλ                          | 7 11        | 7                                                      |

|               | -X Y        |                                   | /" <u>  = :X</u>            | + 9 M2 =    | $\overline{X} + y = M_3 = \overline{X} + \overline{y}$ |

|               | 0 0         | 0                                 |                             |             |                                                        |

|               | 0 1         |                                   | <u>O</u>                    | ]           |                                                        |

|               | 1 0         | <u> </u>                          |                             | 1 0         | 1                                                      |

|               | 1 1         | 1                                 | 1                           |             |                                                        |

|               |             | Maxterm <sub>3</sub>              |                             | = 0         |                                                        |

|               |             |                                   | ر <sup>ح</sup> یون<br>عندها | <u> </u>    | ] 1 2                                                  |

|               |             |                                   |                             |             |                                                        |

| ······        | Ma          | X term : - M                      | axiMam N                    | umber of    | ones                                                   |

|               |             |                                   | distrib                     |             |                                                        |

|               | XF,         | $= M_1 + M_4$                     | + M <sub>7</sub>            |             |                                                        |

|               | ﴿ السي الحق | عد المتغيرات ا                    | lie des p                   | ₩ ←         |                                                        |

|               | ام زی ونا   | Too dist mo                       | عنده المحرد                 | ه کا        |                                                        |

|               |             | varibles                          |                             |             |                                                        |

| <b>C</b>      |             | عون انكم لا                       | •                           |             |                                                        |

| _             |             | •                                 | _                           |             |                                                        |

| 7 1 1 1 1 1 1 |             | [4] è inic                        | بو م                        | ,           |                                                        |

|               |             |                                   |                             |             |                                                        |

| .,            |             |                                   |                             |             |                                                        |

| No.                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Punction) [ Evi i, TZ, off rows ) 1 =                                                                                                                                    |

| $F(A,B,C,D,E) = m_2 + m_3 + m_{17} + m_{23}$                                                                                                                             |

| function = 1 -> 41                                                                                                                                                       |

| $j = j_0 = j_0 = raws 11 se \times 2 = 32 - 4 = 28$                                                                                                                      |

| $2 = 32 - 4 = 28$ $2 = 32 - 4 = 28$ $4 + (X,y) = X + \overline{X} + \overline{Y} + 80P$                                                                                  |

| x y f                                                                                                                                                                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                     |

| $= \frac{X \cdot (\overline{z}y + \overline{y}) + (\overline{x} \cdot \overline{y})}{= Xy + X \cdot \overline{y} + \overline{x} \cdot \overline{y}}$ $= M_3 + M_2 + M_0$ |

| $= m_{6} + m_{2} + m_{3}$ $= 2m(0, 2, 3)$                                                                                                                                |

|                                                                                                                                                                          |

```

XF(A,B,C) = AO(B+B)O(C+c)+BCO(A+A)

Missing) 20 AND Ja =

· variable

=2 (1,4,5,6,7)

\begin{array}{lll}

\times f(X, y, \overline{Z} = X + \overline{X} \overline{y} \quad \text{"POM"} & \text{Lie odded} \\

&= (X + \overline{X}), (X + \overline{y}) \quad \text{Lie odded} \\

&= (X + \overline{y}) + \text{Himtering} \quad \text{"POS"} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}) + \overline{Z}, \overline{Z} \quad \text{Theom'' of S} \\

&= (X + \overline{y}

T M (213)

product

X f(A,B,C)=(AC'+BC)+A'B' POME

=(A'+c'+B). (B'+c+A)

=(A'+B+c).(A+B'+c) POS, PON

M = · M2 = IT M(2,5)

```

|                                         | Light A O P                    |

|-----------------------------------------|--------------------------------|

|                                         | movement, i                    |

|                                         | A R F                          |

|                                         | 0 0 0                          |

|                                         | 0 ) \                          |

|                                         | 1 0 0                          |

|                                         | 1 1 0                          |

|                                         |                                |

|                                         | *A'B'C + A                     |

|                                         | =A+B'C                         |

|                                         |                                |

|                                         | ⇒ Gate Input Cost €            |

|                                         |                                |

|                                         | ABC+D                          |

| *************************************** |                                |

| <i>~</i>                                | Single literal wires 11 amin x |

|                                         |                                |

|                                         | ternais Sib getes la           |

|                                         |                                |

| ()                                      | F=BD+AB'C+ABCP'                |

|                                         | G=11 , GN=14                   |

|                                         | mini mum GN                    |

|                                         | الأدم لل                       |

|                                         | Prosit least cosit             |

|                                         |                                |

X Cost Criteria El New Circuit : )1 our ison F(A,B,C,P) = (ABCDD'). C single Simplication da 8 gio X  $F(A,B,C) = AB + BC + C \cdot (\overline{A} + \overline{B})$ G=L+4=11 GN=13

X oslistly isophuso c'em

Scanned by CamScanner

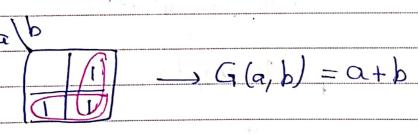

X Karnaugh Maps (k-map)2 g ugers  $\rightarrow$  cells  $F(x, y) = \sum_{m \in xy} m_{xy} = \sum_{xy} m_{x$

adjecent -

1-variable sistail

$$F(x,y) = \mathcal{E}_{m}(2,3) = xy + xy$$

$$= x(y+y)$$

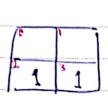

$$X-G(a,b)=a+b$$

=  $E_{1}(1,2,3)$

=  $\overline{X}y + x\overline{y} + \overline{X}y$

=  $\overline{X}y + x(\overline{y} + y)$

$$= \overline{X} y + X$$

$$= X + \overline{X} y$$

$$= X + y$$

\* Three Variable k-Maps -> childrite

m. & m. - adjacent.

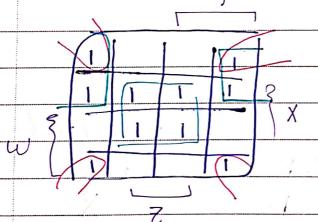

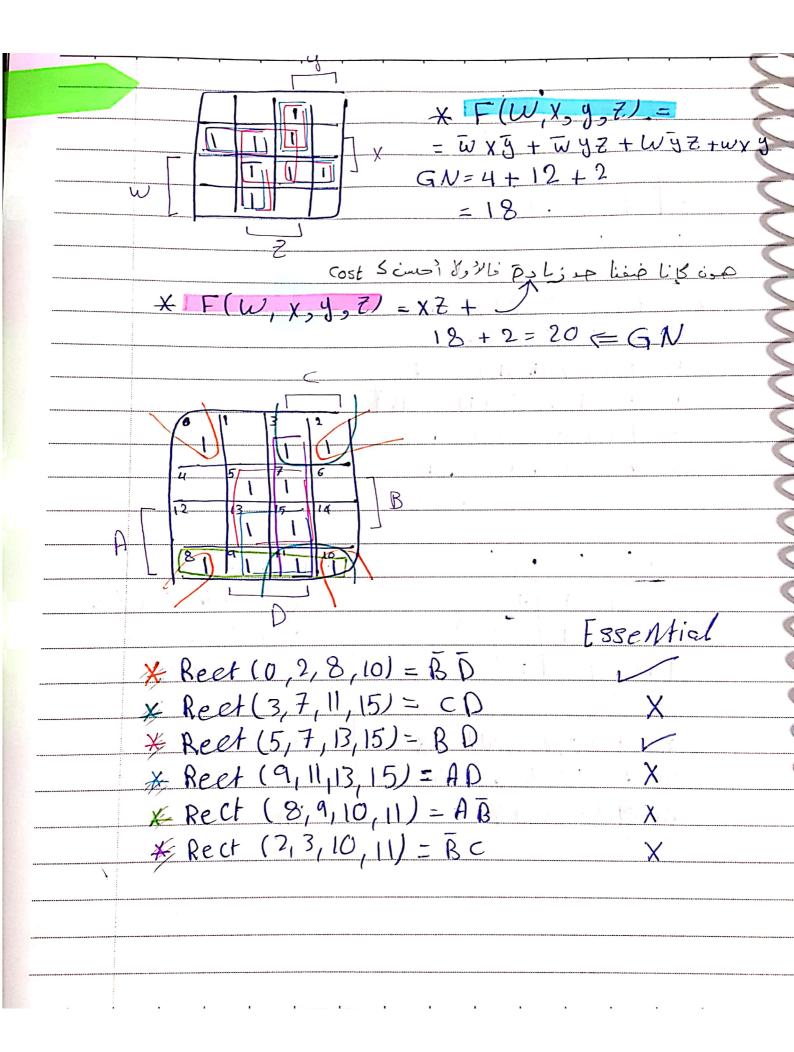

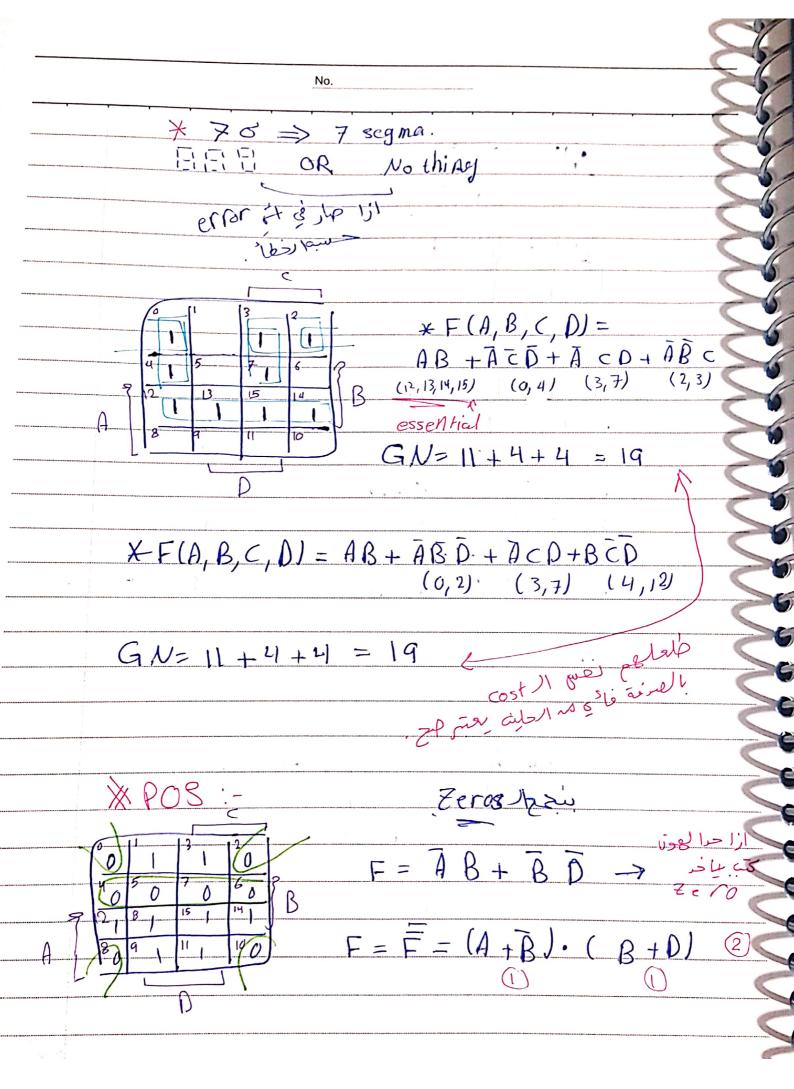

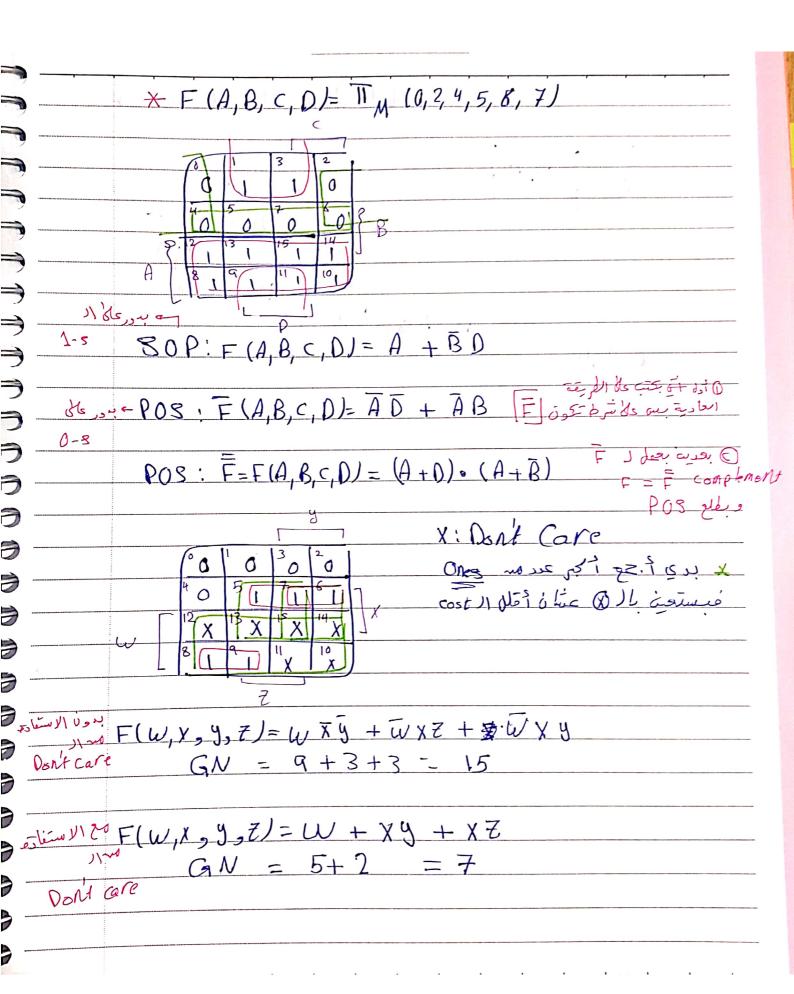

\*Rect (0, 2, 8, 10) =

$$\overline{B}\overline{D}$$

\*Rect (0, 1, 8, 9) =  $\overline{B}\overline{c}$

\*Rect (3, 7, 11, 15) =  $\overline{C}$

\*Rect (4, 6, 12, 14) =  $\overline{B}\overline{D}$

\*Rect (4, 5, 12, 13) =  $\overline{B}\overline{c}$

\* Rect (8,9,10,11) = AB

\* Rect

$$(0,2,8,10) = \overline{X}\overline{Z}$$

\* Rect  $(0,2,4,6) = \overline{W}\overline{Z}$

\* Rect  $(5,7,13,15) = XZ$

$${}^{?} \times F(W, X, Y, Z) =$$

${}^{?} \times F(W, X, Y, Z) =$

${}^{?} \times F(W, X, Y$

$$F(W, y, y, z) = \frac{1}{x^2 + w^2 + x^2}$$

$$\Rightarrow G_{11} = 6 + 3 + 3$$

$$= 1^2$$

| Subject  |                              |             |

|----------|------------------------------|-------------|

| Date     |                              | لااريخ. /   |

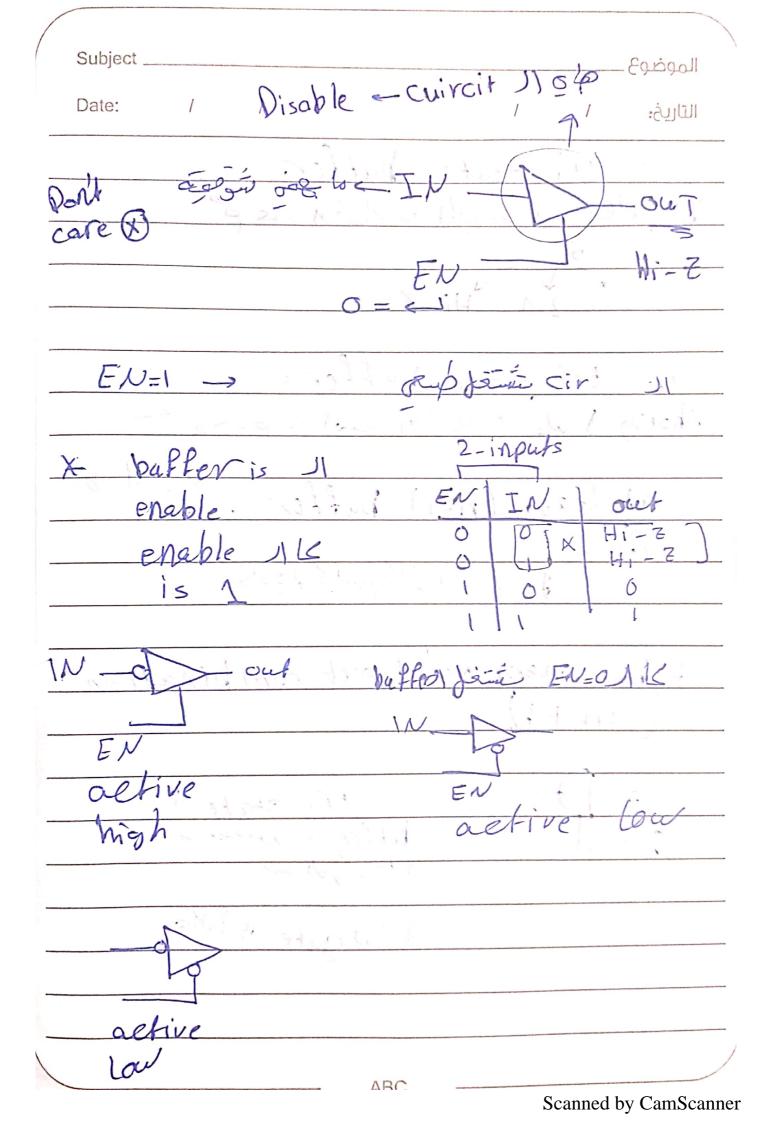

| 2 -      | tri state buffer             |             |

| leli gul | 61 0500 od) EVEN 00 p        | *A-Q        |

| 2        | 5<br>120 Hi-E                |             |

|          | tri state buffers            |             |

|          | Jacks & a los mines no pose. |             |

|          |                              | harlet be   |

| ate      | least (n'-1) buffer          | engle       |

| Hi.      | - 7                          | 11111       |

|          | estrobets d'èl F-il          | <           |

|          |                              | A.          |

| X ho     | w many valid out comb        | ination     |

|          | 2n+1                         |             |

|          |                              |             |

|          | tri state                    | , )         |

| EN       | buffer It state              | 000 M ( ) M |

| •        | يه (لرقر كابه                |             |

|          | Allingate 5?                 | de          |

|          |                              | 30.1        |

Puler Design Fundamentals, 44

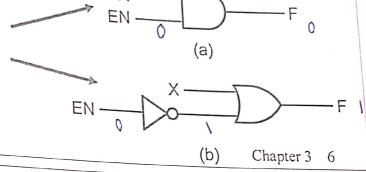

### Tri-State Buffer (3-State Buffer)

For the symbol and truth table, IN is the data input, and EN is the control input

بغضالنظر دلعاًأاً

For (EN = 0) regardless of the value on IN (denoted by X), the wenable output value is Hi-Z Switch It State of Truth Table of Truth Table

For (EN = 1), the output value follows the input value

|    | Symbol |

|----|--------|

| IN | OUT    |

| EN |        |

| ĖN  | ·IN | ÓUT  |

|-----|-----|------|

| . 0 | X   | Hi-Z |

| 1   | 0   | 0    |

| 1   | 1   | 1    |

Chapter 2 - Part 3 14

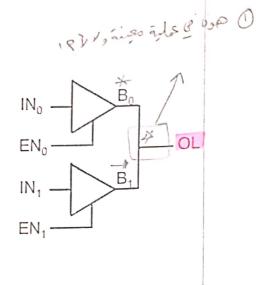

#### Resolving 3-State values on a Connection

Connection of two tri-state buffer outputs,  $B_1$  and  $B_0$ , to a wire, OL (Output Line)  $\rightarrow$  Multiplexed Output

|     | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | *             | ->      | 4            | 48    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|---------|--------------|-------|

| ENI | $EN_{o}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $IN_I$ | $IN_{\theta}$ | $B_I$   | $B_{\theta}$ | OL    |

| 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X      | X             | - Hi- 2 | H7-7         | Hi- Z |

| 0   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X      | 0             | 7-14    | 0            | 0     |

| 0   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X      | 1             | Hi- E   |              | 1     |

| 1   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0      | X             | 0       | Hi-Z         | 0     |

| 1   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1      | X             | 1       | Hi-2         | 1     |

| 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0      | 0             | 0       | 0            | 0     |

| 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1      | 1             | 1       | 1            | 1     |

| 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0      | 1             | 0       | 1            |       |

| 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1      | 0             | (       | 0            |       |

|     | West of the second of the seco |        |               |         |              |       |

#### Resolving 3-State Values on a Conne

Connection of two tri-state buffer outputs, B₁ an wire, OL (Output Line) → Multiplexed Output

-0.

|     | Hi-Z~ Hi-Z > Hi-Z |

|-----|-------------------|

|     | Hi- 2~0 -> 0      |

| ine | Hi-Z~1 → 1        |

| HHL | 0~0 -> 0          |

|     | 1~1 -1            |

| an  | 0~1 ] fire        |

| t   | 1~0 4             |

|        |          |               |                    |          |            |              | 1       |                                                        |

|--------|----------|---------------|--------------------|----------|------------|--------------|---------|--------------------------------------------------------|

|        | $EN_{I}$ | $EN_{o}$      | $IN_I$             | $IN_{0}$ | $B_I$      | $B_{\theta}$ |         | apt 16016                                              |

|        | 0        | 0             | X                  | X        | Hi-Z       | Hi-Z         | Hi-Z    |                                                        |

|        | 0        | 1             | X                  | 0        | Hi-Z       | 0            | 0       | $IN_0 \longrightarrow B_0$                             |

|        | 0        | 1             | X                  | 1        | Hi-Z       | 1            | 1       | FN <sub>2</sub> OL                                     |

|        | 1        | 0             | 0                  | X        | 0          | Hi-Z         | 0       | 2110                                                   |

|        | 1        | 0             | 1                  | X        | 1          | Hi-Z         | 1       | $\left(\begin{array}{c} IN_1 \end{array}\right)$       |

|        | 1        | 1             | 0                  | 0        | 0          | 0            | (0)     | EN <sub>1</sub>                                        |

|        | 1        | 1             | 1                  | 1        | 1          | 1            | U       | A                                                      |

|        | 1        | 1             | $\frac{1}{\theta}$ | 1        | 0          | 1            | Fire    | ما یکونوا در                                           |

|        | 1        | 1             | 1                  | 0        | 1          | 0            | Fire    | Lienie EN 11                                           |

| Danie. | A Deag   | of denon 2 to |                    | منععن    | نتتخلوا مع | in se lo     | ال يوني | اله المحات المستغلم<br>مح بعض<br>Chapter 2 - Part 3 18 |

= [ \*at least (n-1) must be in Hi - 7 Resolving 3-State Values on a Connection 2n+1 = valid 11, sec Resulting Rule: At least one buffer output value must be Hi-Z. Why? • Because any data combinations including (0,1) and (1,0) can occur. If one of these combinations occurs, and no buffers are His Z, then high currents can occur, destroying or damaging the circuit How many valid buffer output combinations exist? → \* 5 valid output combination What is the rule for "n" tri-state buffers connected to Haller one the wire OLP EN=1 At least "n-1" buffer outputs must be Hi-Z How many valid buffer output combinations exist? = Each of the n-buffers can have a or 1 output with all others at Hi-Z Also all buffers can be Hi-Z. So there are 2n + 1 valid combinations. Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> States © 2008 Pearson Education, Inc. Data-Seledor EN ENO alcapion thispx Tri-State Logic Circuit «ctive at the same tine Data Selection Function: If s = 0,  $OL = IN_0$ , else  $OL = IN_1$ Performing data selection with tri-state buffers: Hiz is all firms 5 ( is surrely 2 ) INO EN, IN  $IN_0$  $EN_0$ OL0 0 1 X 0 EN<sub>0</sub> 0 0 1 X 1 1 IN<sub>1</sub> 0 0 X 0 EN X Since  $EN_0 = \overline{s}$  and  $EN_1 = s$ , one of the two buffer outputs is always Hi-Z. one of them will be active S 120 12, Chapter 2 - Part 3

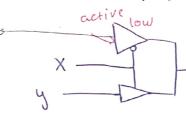

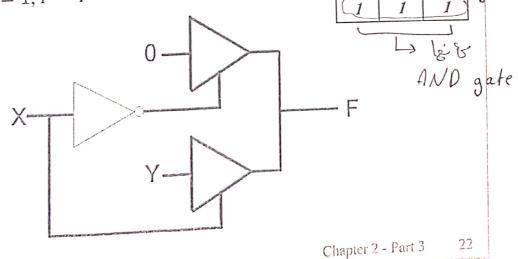

## Logic Functions using Tri-State Buffers

Implement AND gate using 3-State buffers and inverters

| F | (X, | Y) | = | Χ.    | Y |

|---|-----|----|---|-------|---|

|   | , , | /  |   | 4 4 4 | 1 |

Use X as control input:

| L | When | X = | 0, F | = ( | <u>)</u> regai | rdless | of th | ie v | alue | of | Y |

|---|------|-----|------|-----|----------------|--------|-------|------|------|----|---|

|   | ,    |     |      |     | 1              |        |       |      |      |    |   |

| - |      | - |   |    |   |   |   |  |

|---|------|---|---|----|---|---|---|--|

|   | When | X | = | 1, | F | = | Y |  |

|   |     | _          |

|---|-----|------------|

|   | 11  | 11' - /    |

| V | 10- | she of sul |

| X | 00  | 3 li armo  |

| X        | Y | F        |

|----------|---|----------|

| 0        | 0 | $\theta$ |

| $\theta$ | 1 | 0        |

| 1        | 0 | 0        |

| 1        | 1 | 1        |

X de stiratere 1 0 1 0

X de stiratere 1 0 0

I I I I

Variable

active

tow

Chapter 2 - Part 3

### Logic Functions using Tri-State Buffers

Implement AND gate using 3-State buffers and inverters

$$F(X,Y) = X.Y$$

- Use X as control input:

- When X = 0, F = 0 regardless of the value of Y

- When X = 1, F = Y

10 applier Design Fundamentus de

| $\mathcal{X}$ | Y                 | $\boldsymbol{\mathit{F}}$ |   |      |   |

|---------------|-------------------|---------------------------|---|------|---|

| 0             | 0                 | 0                         | 7 | F= X |   |

| 0             | 1                 | 0                         | 7 | F- X |   |

| 1             | 0                 | 0                         | 7 | F=   | 4 |

| 1             | 1                 | 1                         | 7 |      |   |

| ·             |                   |                           |   |      |   |

|               | $\hookrightarrow$ | لون في                    |   |      |   |

Scanned by CamScanner

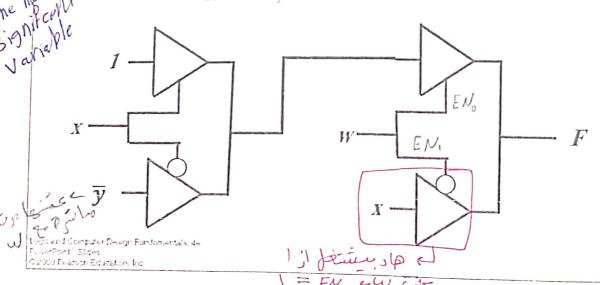

## Logic Functions using Tri-State Buffers

Implement the following function using 3-State buffers

and inverters:  $F(w, x, y) = \overline{w}x + w\overline{y} + xy$

Use was control input: by as so

When w = 0, F = x regardless of the value of Y

| • 14 | hen | $\overline{W}$ | = | 1 |

|------|-----|----------------|---|---|

|------|-----|----------------|---|---|

If

$$x = 0$$

,  $F = \bar{y}$

$$= If x = 1, F = 1$$

| W | X | y | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

Chapter 2 - Part 3

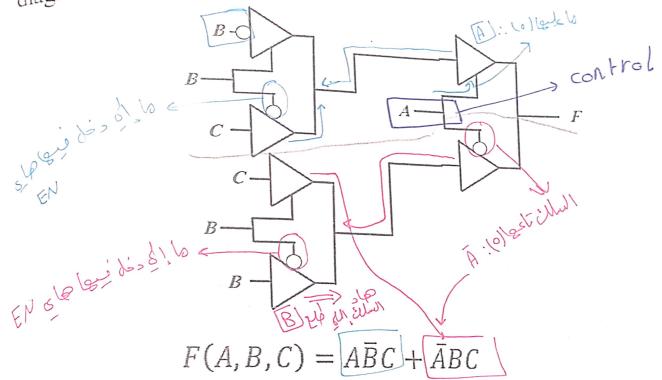

## Logic Functions using Tri-State Buffers

Write the Boolean expression of F(A, B, C) given the diagram below:

rd Computer Design Fundamentalis, 4e pirf Sides Passon Education, Inc.

Chapter 2 - Part 3

25

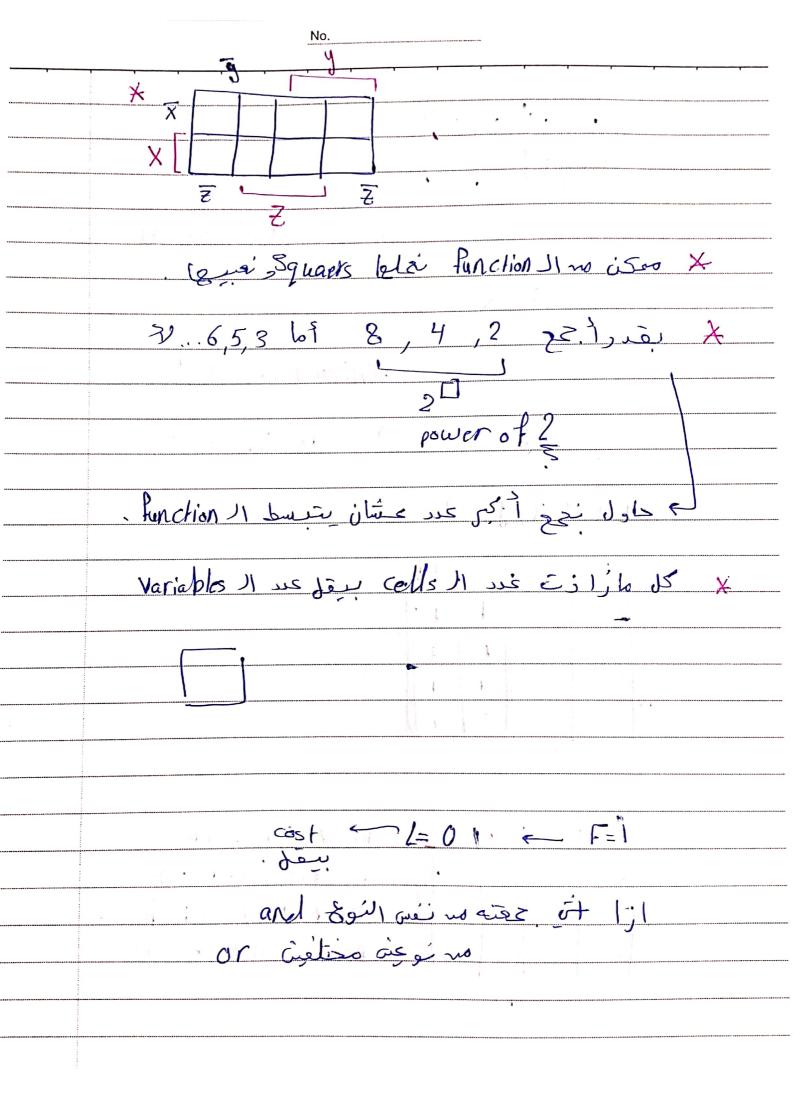

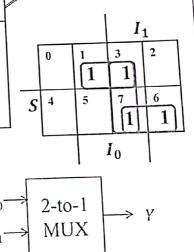

## Odd and Even Functions

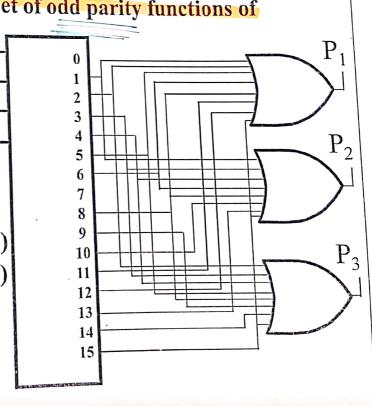

The 1s of an *odd function* correspond to minterms having an index with an odd number of 1s.

|     |   | ( | 10c | )   | , 6 | 110 |

|-----|---|---|-----|-----|-----|-----|

|     |   | 0 | 1   | 3   | 2   |     |

|     | x | 4 | 5   | 7   | 6   |     |

| 100 | 4 | 1 |     |     |     |     |

|     |   |   |     | 111 | ı   |     |

|     |    |    | (  | :  |   |  |

|-----|----|----|----|----|---|--|

|     | 0  | 1  | 3  | 2  |   |  |

|     |    | 1  |    | 1  |   |  |

|     | 4  | 5  | 7  | 6  |   |  |

|     | 1  |    | 1  |    |   |  |

|     | 12 | 13 | 15 | 14 | B |  |

| A   |    | 1  |    | 1  |   |  |

| 4.4 | 8  | 9  | 11 | 10 |   |  |

|     | 1  |    | 1  |    |   |  |

|     | D  |    |    | _  |   |  |

The 1s of an *even function* correspond to minterms having an index with an even number of 1s.

| 000 |   |        | 011 | , |

|-----|---|--------|-----|---|

|     | 0 | I      | 3   | 2 |

| x   | 4 | 5<br>1 | 7   | 6 |

|     |   | 2      | Z   |   |

| ,                  |     |     | C       | ;  |    |

|--------------------|-----|-----|---------|----|----|

|                    | 0 1 | 1   | 3       | 2  |    |

|                    | 4   | 5   | 7       | 6  |    |

| . 1                | 12  | 13  | 15<br>1 | 14 | В  |

| · A                | 8   | 9 1 | 11      | 10 |    |

|                    |     |     | D       |    |    |

| Chapter 2 - Part 3 |     |     |         |    | 34 |

l Copular Design Fundamentials, de d<sup>i</sup> Sistes wich Educaton, Ive

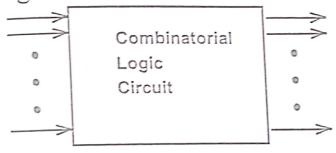

## Combinational Circuits

- A combinational logic circuit has:

- A set of m Boolean inputs,

- , A set of n Boolean outputs, and

- switching functions, each mapping the 2m input combinations to an output such that the current output depends only on the current input values

- A block diagram:

m Boolean Inputs

n Boolean Outputs

Chapter 3 - Part 1

### Design Procedure

#### تحصيف المواجئات 1. Specification

Write a specification for the circuit if one is not already available. What does the circuit do? Including names or symbols for inputs and outputs

#### 2. Formulation

- Derive a truth table or initial Boolean equations

- that define the required relationships between the inputs and outputs, if not in the specification

#### 3. Optimization

- Apply 2-level optimization using K-maps

- Draw a logic diagram for the resulting circuit using ANDs, ORs, and inverters

# Design Procedure

4. Technology Mapping

Map the logic diagram to the implementation

Map the logic doctor technology selected

5. Verification

5. Verification

The second design of the final d

Logic and Computer Design Fundamentals, 4e Fraesthant<sup>®</sup> Skiles © 2008 Pearson Education, Inc. Chapter 3 - Part 1

## Design Example1

Specification: Design a combinational circuit that has 3 inputs (X, Y, Z) and one output F, such that F = 1 when the number of 1's in the input is greater than the number of 0's (i.e. number of 1's  $\geq 2$ )

• This is called *majority function* (i.e. majority of inputs must be for the function to be 1)

Formulation: Zeil 26, 013 05

| X   | Y  | Z   | F  |

|-----|----|-----|----|

| 0   | 0  | 0   | 0  |

| 0   | 0  | 1   | 0  |

| 0   | 1  | 0   | .0 |

| 0   | i  | 1)  | 1  |

| 1   | 0  | 0   | 0  |

| (i) | 0  | (1) | 1  |

| 1   | Ĩ) | Q   | 1  |

| 1   | 1) | 1   | 1  |

Logic and Computer Design Fundamentals, 4± Foxed reint Folder D 2008 Painton Education Inc.

Scanned by CamScanner

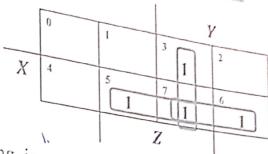

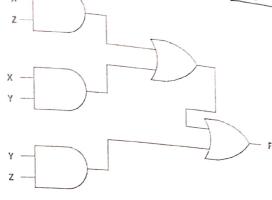

Optimization:

$$(X,Y,Z) = XY + XZ + YZ$$

, Technology Mapping:

Mapping with a library containing inverters, 2-input AND, 2-input

Chapter 3 - Part 1

## Design Example2

بعوی اهن بیعطین رمج Specification:-Design a combinational م circuit that compares 2-bit Binary number (A, B) and produce two outputs  $(O_1, O_0)$ , such that:

| $0_10_0 = 00$ | When $A = B$ and Both are even |

|---------------|--------------------------------|

| $0_10_0 = 01$ | When $A < B$                   |

| $0_10_0 = 10$ | When $A > B$                   |

| $0_10_0 = 11$ | When $A = B$ and Both are odd  |

' Formulation:

| 1 89         | جه          | C               | 11 Jan 1 | 11         |

|--------------|-------------|-----------------|----------|------------|

| 1            | $A(A_1A_q)$ | $B(B_1B_{\nu})$ | 0(0,00)  | //         |

| 0            | 00          | 00              | 00       | -          |

| 1            | 00          | 01              | 01 7     | ٨          |

| 2            | 00          | 10              | 01       | BZH        |

| 2            | 00          | 11              | 01       |            |

|              | 01          | 00              | 10       | A7B<br>A=B |

| `4<br>5<br>6 | 01          | 01              | 11       | = A=B      |

| 6            | . 01        | 10              | 01       |            |

| 7            | 01          | 11              | 01       |            |

| 1-8          | 10          | 00              | 10       |            |

| 9            | 10          | 01              | 10       |            |

| 10           | 10          | 10              | 00       | 4          |

| , 11         | 10          | 11              | 01       |            |

| 1/2          | 11          | 00              | 10       |            |

| 13           | 11          | 01              | 10       | -          |

| 14           | 11          | 10              | 10       |            |

| 15           | 11          | 11              | 11       |            |

|              |             |                 |          |            |

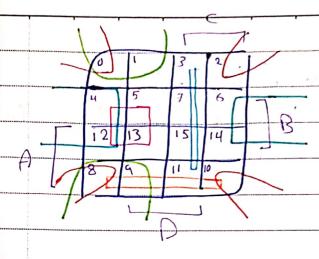

## Design Example2 Cont.

Optimization and Technology Mapping:

16 \* 2 = 32

اناها کله فاشد 2- K map

| O <sub>0</sub> | Colonia de Aspendo Perio des esta esta esta esta esta esta esta es |        | В       | 1              |

|----------------|--------------------------------------------------------------------|--------|---------|----------------|

|                | 0                                                                  | 1      | 3 1     | 1              |

|                | 4                                                                  | 5<br>1 | 7       | 6              |

|                | 12                                                                 | 13     | 15<br>1 | 14 A 0         |

| $A_1$          | 8                                                                  | 9      | 11      | 10             |

|                |                                                                    | I      | 30      |                |

| $O_1$          |                                                                    |        | 1       | B <sub>1</sub> |

|                | 0                                                                  | 1      | 3       | 2              |

|                | 4                                                                  | 5      | 7       | 6              |

|                | 12                                                                 | 13     | 15      | 14             |

| $A_1$          | 8                                                                  | 9      | 11      | 10             |

|                |                                                                    |        | $B_0$   |                |

Chapter 3 - Part 1

mputer Design Fundamentals, 4e Slides on Education, Inc.

## Design Example2 Cont.

Optimization and Technology Mapping:

$$O_1 = A_1 A_0 + A_0 \overline{B_1} + A_1 \overline{B_1}$$

| $O_0$ |    |    | B   | 1              |       |

|-------|----|----|-----|----------------|-------|

|       | 0  | 1  | 1   | 1              |       |

|       | 4  | 5  | 7 1 | 6              | 1     |

|       | 12 | 13 | 1:1 | 14             | $A_0$ |

| $A_1$ | 8  | 9  | 11  | 10             |       |

|       |    | В  | 0   |                |       |

| 0,    | ,  |    |     | B <sub>1</sub> |       |

| 1     | 0  | 1  | 3   | 2              |       |

| O       | •   |    | B     | 1  | ,     |

|---------|-----|----|-------|----|-------|

|         | 0   | 1  | 3     | 2  |       |

|         | 1   | -5 | 7     | 6  | 1     |

|         | 1   | 1  | 1     | 1  | $A_0$ |

| $A_{j}$ | 1 8 | 9  | 11    | 10 |       |

|         |     |    | $B_0$ |    |       |

. Chapter 3 - Part 1

12

### Design Example3

#### 1. Specification

Pular Design Full discontinue d

n Education, Inc

- BCD to Excess-3 code converter <-

- Transforms BCD code for the decimal digits to Excess-3 code for the decimal digits

- BCD code words for digits 0 through 9: 4-bit patterns 0000 to 1001, respectively

- Excess-3 code words for digits 0 through 9: 4-bit patterns consisting of 3 (binary 0011) added to each BCD code word

- · BCD input is labeled A, B, C, D

- Excess-3 output is labeled W, X, Y, Z

# Design Example3 Cont.

|                                                  | and the second s |      |                    |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|

|                                                  | ABCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WXYZ |                    |

| 2. Formulation                                   | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0011 |                    |