Problem 1. Solve the following short problems.

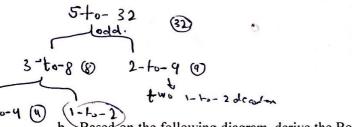

a. In order to build a 5-to-32 line decoder, we will need \_\_\_\_\_\_ 2-input AND gate(s) and \_\_\_\_ 1-to-2 line decoder(s).

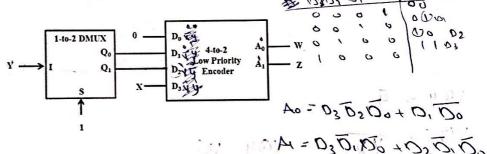

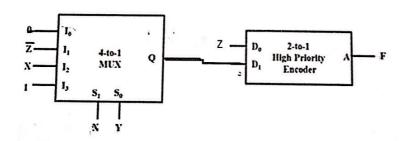

b. Based on the following diagram, derive the Boolean expression of W and Z outputs as functions

$$W(X,Y) = \chi \overline{y} + 0$$

$$Z(X,Y) = \chi \chi y$$

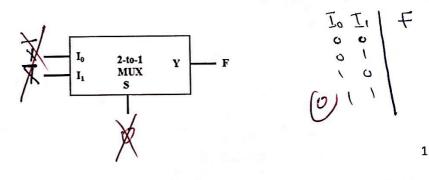

c. Implement the function  $F(X) = \overline{X}$  using <u>only</u> the following 2-to-1 multiplexer.

- d. Given that N is 6-bit <u>signed</u> number with value (11010)<sub>2</sub>. What would be the <u>binary</u> value of (-N) for each of the following signed number representations?

- Sign-magnitude

II. 1's complement

III. 2's complement

| -N = ( | 111   | c) | 1 | 1 | 1/2         |

|--------|-------|----|---|---|-------------|

| ,      | 1 1 1 | _  | • | • | S. Constant |

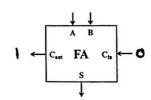

e. Given the following full adder cell, if  $C_{in} = 0$  and  $C_{out} = 1$ , then the values of A and B are:

X04= X9+ X9

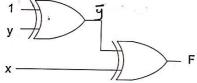

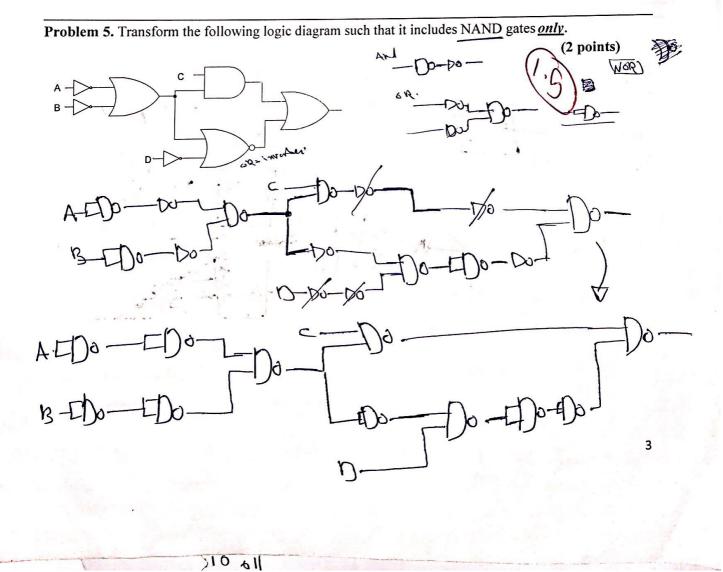

Problem 2. Show that the following circuit implements a 2-input XNOR gate.

**Problem 3.** Based on the following logic diagram, fill the truth table for function F(X,Y,Z). (2 points)

| X | Y | Z |   | F |

|---|---|---|---|---|

| 0 | 0 | 0 |   | 3 |

| 0 | 0 | 1 | 1 |   |

| 0 | 1 | 0 |   | X |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   | 1 |

| 1 | 1 | 0 |   | 1 |

| 1 | 1 | 1 |   |   |

Problem 4. It is required to design a logic circuit whose input is a value between 0 and 7 and outputs the result of the integer division between the input value and 3. For example, if input is 7, then the output is 2 and when the input is 3, then the output is 1. <u>Draw and fill the truth table of the circuit. Don't derive</u>

the expression(s) for the output(s)

(4 points)

Problem 6. Design the combinational logic circuit of function F(X,Y) using the given 3-to-8 line decoder with enable and the AND gate. You can add any number of inverters. (3 points)

$\sum_{x} F(X,Y) = \sum_{x} (0,3)$

Hint: You must label all decoder inputs clearly.

TTM (1,2)

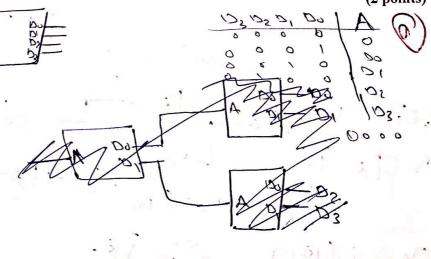

Problem 7. Design a 1-to-4 demultiplexer using <u>only</u> 1-to-2 demultiplexers. You must label all inputs and outputs clearly. (2 points)

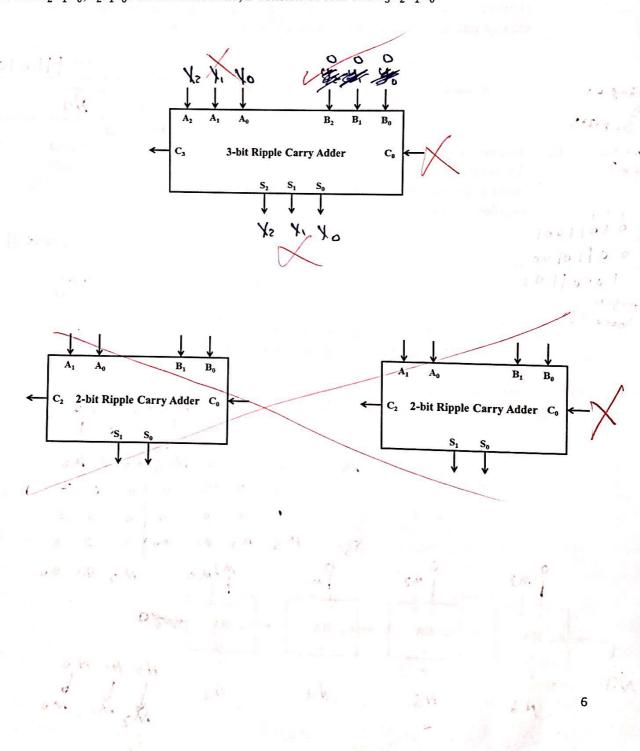

Problem 10. Assume X and Y are 3-bit <u>signed 2's complement</u> numbers. Using <u>only</u> the following 3-bit and 2-bit ripple carry adders and any number of XOR gates, design a circuit that outputs a 4-bit <u>signed</u> <u>2's complement</u> number Z such that:

(3 points)

where

$$|Y| = \begin{cases} Y, when Y \ge 0 \\ -Y, when Y < 0 \end{cases}$$

<u>Hint:</u> You must show clearly all connections and labeling. Keep in mind that each of X and Y consists of three bits  $X_2X_1X_0$ ,  $Y_2Y_1Y_0$ . On the other hand, Z consists of four bits  $Z_3Z_2Z_1Z_0$ .