LOGIC Managering

Estan Ahmad AL-Ajour

Computer Engineering

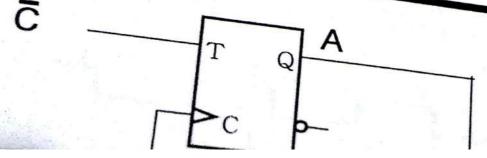

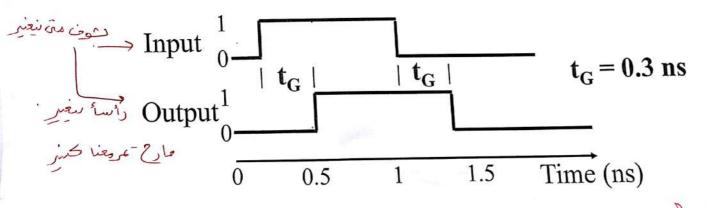

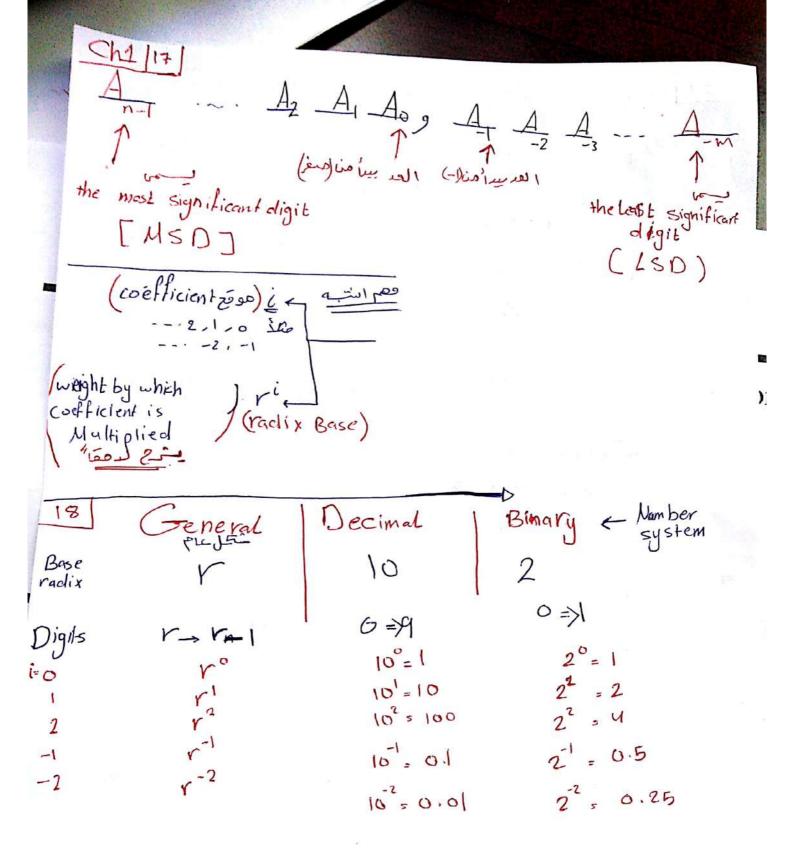

### **Gate Delay**

- In actual physical gates, if one or more input changes causes the output to change, the output change does not occur instantaneously

- The delay between an input change(s) and the resulting output change is the *gate delay* denoted by  $t_G$ :

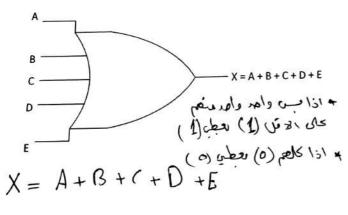

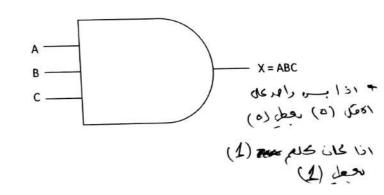

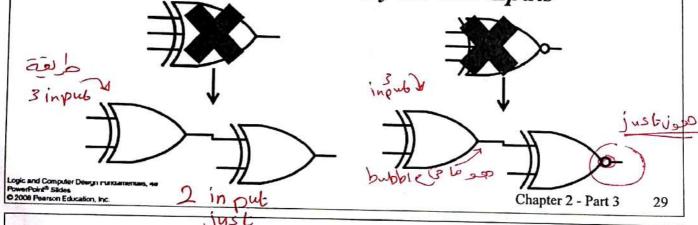

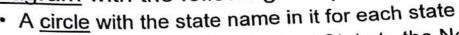

# Logic Gates: Inputs and Outputs

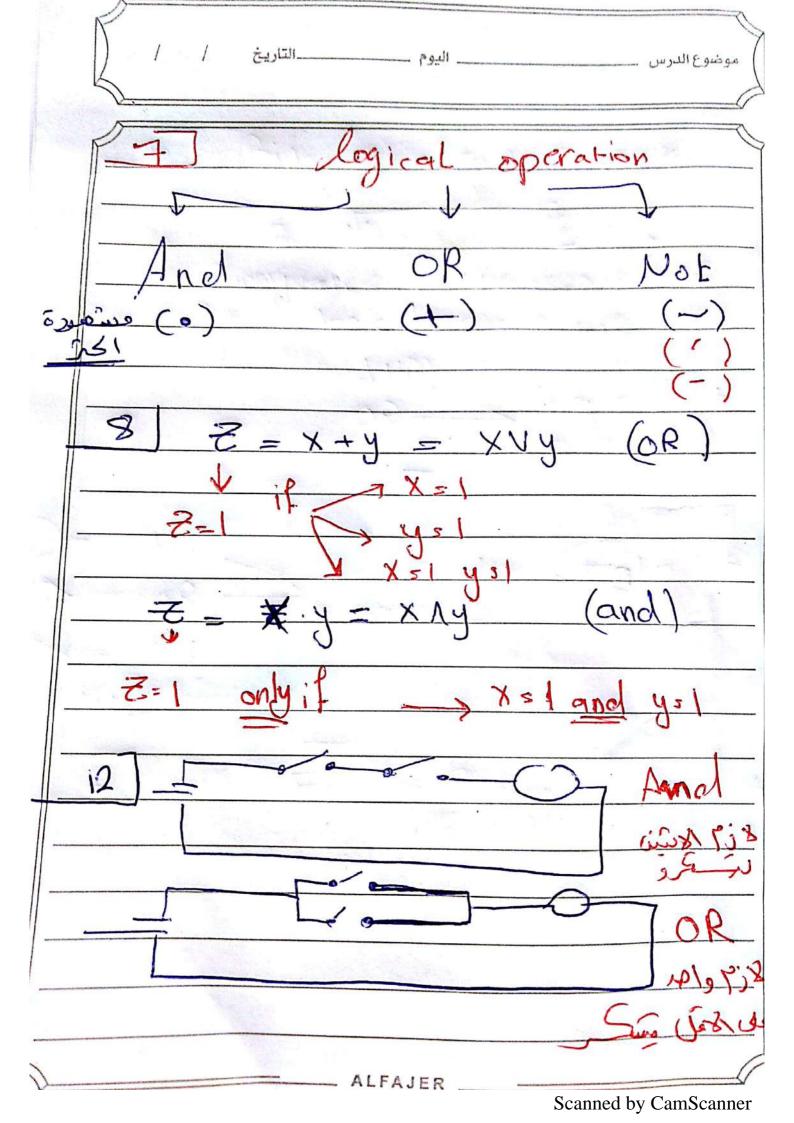

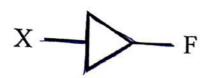

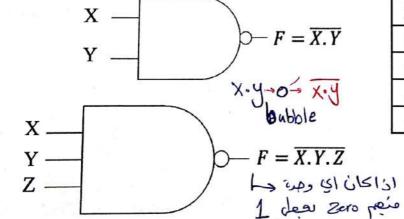

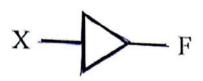

NOT (inverter)

لازم واهم فقط رحمون

- · Always one input and one output

- AND and OR gates

واحداواكير

- · Always one output

- · Two or more inputs

Logic and Computer Design Fundamentals, 4e

Chapter 2 - Part 1

18

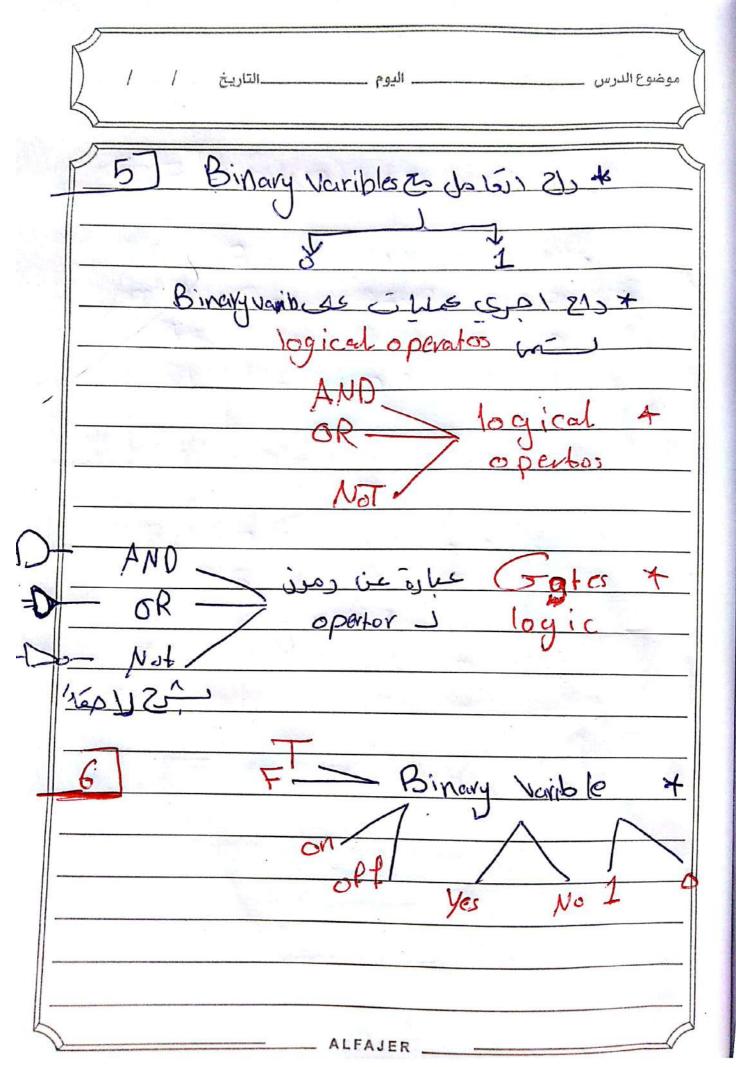

### Boolean Algebra

- An algebra dealing with binary variables and logic operations

- · Variables are designated by letters of the alphabet

- Basic logic operations: AND, OR, and NOT

- A Boolean expression is an algebraic expression formed by using binary variables, constants 0 and 1, the logic operation symbols, and parentheses

• E.g.:

$$X.1$$

,  $A+B+C$ ,  $(A+B)(C+D) \rightarrow B$  or lear expersion

■ A Boolean function consists of a binary variable identifying the function followed by equals sign and a Boolean expression

• E.g.

$$F = A + B + C$$

,  $L(D, X, A) = DX + \bar{A} \rightarrow B$  Ballean function

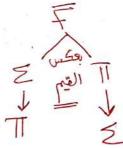

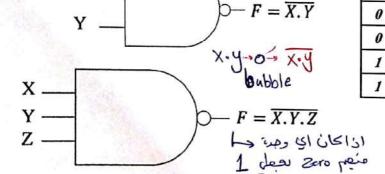

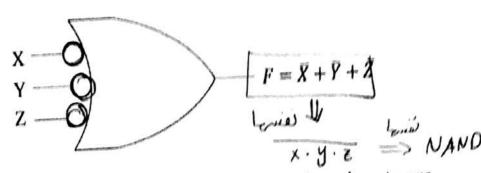

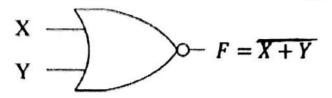

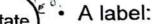

### Logic Diagrams and Expressions

2. Logic Diagram:

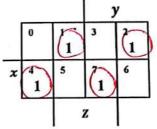

| XYZ   | 0  |

|-------|----|

| 0 0 0 | 1  |

| 0 1 0 | 0  |

| 0 1 1 | 0  |

| 100   |    |

| 101   | i_ |

| 110   | ι  |

| 111   | 1  |

الاكني 1

16/21

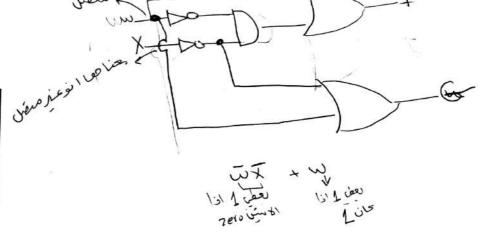

البائي داع يطلح مين صين تو X + 0 + X اذا كانت

Chapter 2 - Part 1

20

23

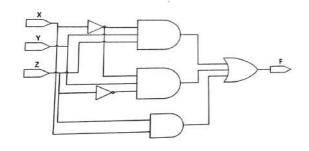

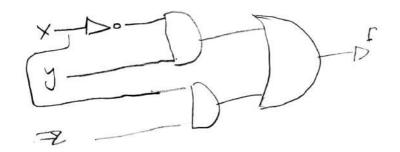

Boolean function:  $F(W, X, Y) = XY + W\overline{Y}$

Logic Diagram:

Truth Table.

| W   | / X | Y  | F |

|-----|-----|----|---|

| 0   | 0   | į0 | 0 |

| 0   | 0   | 1  | 0 |

| 0   | 1   | Ó  | ۵ |

| -0  | 1   | 1  | ١ |

| 1   | 0   | 0  | 1 |

| 1   | 0   | 1  | 0 |

| - 1 | 1   | 0  | 1 |

| 1   | 1   | 1  | 1 |

علی الکنو بعطی م الکنو بعطی م الکوان (1) لانو بعطی م الکوان (1) لانو بستم می المون کرد به معلی 1 ایک نویسطی م المون کرد به محلی (1) لانو بستعم کی المون کرد بستان به محلی (1) لانو بستعم کی المون بستان کرد ب

This example represents a Single Output Function

■ Draw the logic diagram and the truth table of the following Boolean functions:  $F(W,X) = \overline{W}\overline{X} + W, G(W,X) = W + \overline{X}$

Logic Diagram:

Truth Table:

| W | X | F | G |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | D |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

ign rundamenas, +e

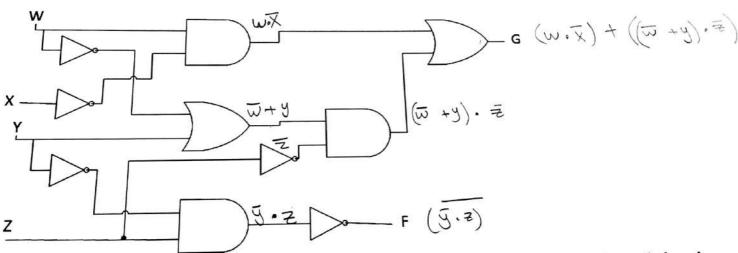

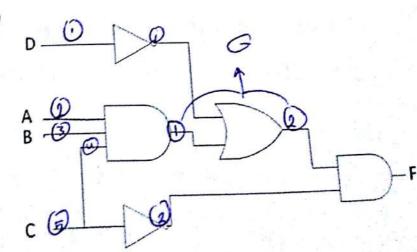

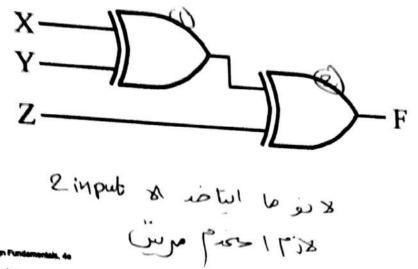

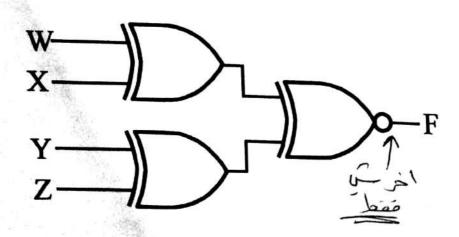

Given the following logic diagram, write the corresponding Boolean equation:

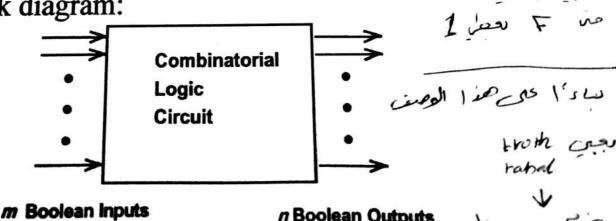

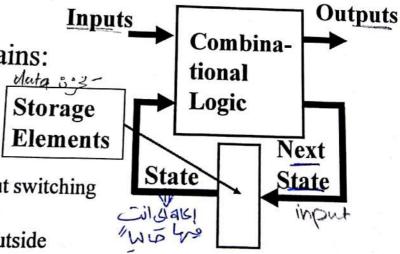

Logic circuits of this type are called combinational logic circuits since the variables are combined by logical operations

d Computer Design Fundamentals, 4e

### ic Identities of Boolean Algebra

عا ارتفاعل عمر اللوجيل في احسياد ثابت دشسا حد على م تنبسيع و الفاقع

| 1. $X + 0 = X$                                                                                                                                                                             | 2 4 4 4                                                                                                         |                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                                                                                                                                            | 2. X.1 = X                                                                                                      | Existence of 0 and 1    |

| [3. X+1=1]                                                                                                                                                                                 | 4. X.0 = 0                                                                                                      | Existence of 0 and 1    |

| 5. $X + X = X - \begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \end{bmatrix}$                                                                                                                      | 6. X . X = X                                                                                                    | Idempotence             |

| 7. $X + \overline{X} = \bigcirc $ | $8. X.\overline{X} = \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc \bigcirc$ | Existence of complement |

| 9. $\overline{X} = X \times \sqrt[3]{x} = X$                                                                                                                                               |                                                                                                                 | Involution              |

| 10.X + Y = Y + X ترقیب ما بغرف                                                                                                                                                             | كريبَ ما فرق ك YX €YX                                                                                           | Commutative Laws        |

| (2.(X + Y) + Z = X + (Y + Z))                                                                                                                                                              | 13.(XY)Z = X(YZ)                                                                                                | Associative Laws        |

| 4.X(Y+Z) = XY + XZ مندح                                                                                                                                                                    | 15.X + (YZ) = (X + Y)(X + Z)                                                                                    | Distributive Laws       |

| $6.\overline{X+Y} = \overline{X}.\overline{Y}$ Demorgians                                                                                                                                  | $17.\overline{X}.\overline{Y} \supseteq \overline{X} + \overline{Y}$                                            | DeMorgan's Laws         |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

## Some Properties of Identities & the Algebra

- If the meaning is unambiguous, we leave out the symbol

- The identities above are organized into pairs

- The dual of an algebraic expression is obtained by interchanging (+) and (·) and interchanging 0's and 1's

The identities appear in dual pairs. When there is only one identity on a line the identity is self-dual, i. e., the dual expression = the

original expression.

Chapter 2 - Part 1

Logic and Computer Design Fundamentals, 4e erPoint® Stides © 2008 Pearson Education, Inc.

### Some Properties of Identities & the Algebra (Continued)

- Unless it happens to be self-dual, the dual of an expression does not equal the expression itself

- Examples:

•

$$F = (A + \overline{C}) \cdot B + 0$$

•  $Dual F = (A \cdot \overline{C}) + B \cdot (A \cdot \overline{C})$

•

$$G = XY + (\overline{W + Z})$$

•  $Dual G = (X + Y) \cdot (\overline{W + Z}) = (X + Y) \cdot (\overline{W + Z})$

•

$$H = AB + AC + BC$$

•  $Dual H = (A + B) \cdot (A + C) \cdot (B + C)$

Are any of these functions self-dual?

۱د ا لهلع نعندی الاملم میخ نامرو ک

Collable o light res

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Sildes © 2008 Pearson Education, Inc.

#### Some Properties of Identities & the Algebra (Continued)

- Unless it happens to be self-dual, the dual of an expression does not equal the expression itself

- Examples:

- $F = (A + \bar{C}) \cdot B + 0$

- Dual  $F = ((A \cdot \overline{C}) + B) \cdot 1 = A \cdot \overline{C} + B$  (Accurate)

- $G = XY + (\overline{W + Z})$

- Dual  $G = (X + Y).\overline{WZ} = (X + Y).(\overline{W} + \overline{Z})$

- H = AB + AC + BC

- Dual H = (A + B)(A + C)(B + C) = (A + BC)(B + C)

- =AB + AC + BC

- Are any of these functions self-dual?

Logic and Computer Design verPoint® Slides

# **Boolean Operator Precedence**

- The order of evaluation in a Boolean expression is:

- Parentheses | 6-1568

- 2. **NOT**

- 3. <u>AND</u>

- 4. **QR**

- Consequence: Parentheses appear around OR expressions

•

$$F = A(B+C)(C+D)$$

- F = A(B+C)Logic and Computer Design Fundamentals, 4e

PowerPoint® Slides

• Examples:

•  $F = A(B + C)(C + \overline{D})$ • F = AB + C• F = AB + C

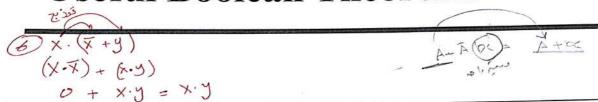

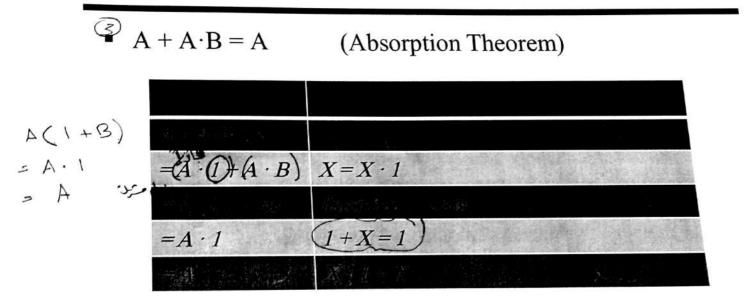

### **Useful Boolean Theorems**

| Theorem                        | Dual                     | Name           |

|--------------------------------|--------------------------|----------------|

| $\bigcirc x.y + \bar{x}.y = y$ | $(x+y)(\bar{x}+y)=y$     | Minimization   |

| $3 x + x \cdot y = x$          | x.(x+y) = x              | Absorption     |

|                                | $x.(\bar{x}+y)=x.y$      | Simplification |

| $x.y + \bar{x}.z + y$          | $y.z = x.y + \bar{x}.z$  | Consensus      |

| $(x+y)(\bar{x}+z)(y+$          | $-z) = (x+y)(\bar{x}+z)$ | 1 1 1 (4.2)    |

Chapter 2 - Part 1

Logic and Computer Design Fundamentals. PowerPoint® Slides

Scanned by CamScanner

### **Example 1: Boolean Algebraic Proof**

- Our primary reason for doing proofs is to learn:

- Careful and efficient use of the identities and theorems of Boolean algebra

- How to choose the appropriate identity or theorem to apply to make forward progress, irrespective of the application

Logic and Computer Design Fundamentals, 4e

# **Example 2: Boolean Algebraic Proofs**

| * | $AB + \bar{A}C + BC = AB + \bar{A}C$ | (Consensus Theorem) |

|---|--------------------------------------|---------------------|

|   |                                      |                     |

| Frod Steps                                              | Justification (identity by theorem) |

|---------------------------------------------------------|-------------------------------------|

| $AB + \overline{A}C + BC$                               |                                     |

| $= AB + \overline{A}C + \widehat{1}BC$                  | 1. X = X                            |

| $=AB+\overline{A}C+(A+\overline{A}).\overline{B}C$      | $X + \overline{X} = 1$              |

| $=AB+\overline{A}C+ABC+\overline{A}BC$                  | Distributive Law                    |

| $= AB + ABC + \overline{A}C + \overline{A}BC$           | Commutative Law                     |

| $= AB. 1 + AB. C + \overline{A}C. 1 + \overline{A}C. B$ | X.1 = X and Commutative Law         |

| $=AB(1+C)+\overline{A}C(1+B)$                           | Distributive Law                    |

| $=AB.1+\overline{A}C.1$                                 | 1+X=1                               |

| $=AR+\overline{AC}$                                     | X.1 = X                             |

Logic and Computer Design Fundamentals, 4e

# **Proof of Simplification**

$A + \bar{A} \cdot B = A + B$  (Simplification Theorem)

| $A + \bar{A}.B$     |                              |

|---------------------|------------------------------|

| $=(A+\bar{A})(A+B)$ | Distributive law             |

| - 2.4 7.50          | Anetro Premis Description en |

|                     |                              |

$= (A + B) X + \overline{X} = 1$   $A. (\overline{A} + B) = AB (Simplification Theorem)$

| $A.(\bar{A}+B)$      |                  |  |

|----------------------|------------------|--|

| $=(A.\bar{A})+(A.B)$ | Distributive Law |  |

| = 0 + AB             | $X.\bar{X}=0$    |  |

| =AB                  | X + 0 = X        |  |

Chapter 2

### **Proof of Minimization**

$$A.B + \bar{A}.B = B$$

(Minimization Theorem)

$$A. B + \overline{A}. B$$

$$= B(A + \overline{A})$$

$$= B. 1$$

$$= B. 1$$

$$= B. X. 1 = X$$

$$X. 1 = X$$

$$(A + B)(\bar{A} + B) = B$$

(Minimization Theorem)

$$(A + B)(\bar{A} + B)$$

$$= B + (A \cdot \bar{A})$$

$$= B + 0$$

$$= B$$

$$= B$$

$$= B$$

$$X \cdot \bar{X} = 0$$

$$X \cdot \bar{X} = 0$$

$$X \cdot \bar{X} = 0$$

Chapter 2

### Proof of DeMorgan's Laws (1)

- $\overline{X+Y} = \overline{X}.\overline{Y}$  (DeMorgan's Law)

- We will show that,  $\overline{X}.\overline{Y}$ , satisfies the definition of the complement of (X + Y), defined as  $\overline{X} + \overline{Y}$  by DeMorgan's Law.

- To show this, we need to show that A + A' = 1 and  $A \cdot A' = 0$  with A = X + Y and  $A' = X' \cdot Y'$ . This proves that  $X' \cdot Y' = X + Y$ .

Part 1: Show  $X + Y + X' \cdot Y' = 1$

(X+Y+X) (X+Y+Y) (X+Y+X) (X+Y+Y) (X+Y)

Chapter 2 - Part 1

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides

# Proof of DeMorgan's Laws (2)

Part 2: Show (X + Y).X'.Y' = 0

$$(x,y)$$

+  $(y,y,x)$  = 0

$(0.9)$  +  $(0.7)$  = 0

- Based on the above two parts,  $X' \cdot Y' = \overline{X + Y}$

- The second DeMorgans' law is proved by duality

- Note that DeMorgan's law, given as an identity is not an axiom in the sense that it can be proved using the other identities.

Computer Design Fundamentals, 4e R<sup>®</sup> Stides

## Example 3: Boolean Algebraic Proofs

$$\overline{(X+Y)Z+X\overline{Y}} = \overline{Y}(X+Z)$$

$$((\overline{X},\overline{y}) \neq + \overline{X}\overline{y})$$

$$((\overline{X},\overline{y}) \neq + \overline{X}\overline{y})$$

$$\overline{y}(\overline{X} \neq + \overline{X})$$

$$\overline{y}(\overline{Z} + \overline{X}) = \overline{y}(X+\overline{z})$$

$$\overline{y}(\overline{Z} + \overline{X}) = \overline{y}(X+\overline{z})$$

$$\overline{y}(\overline{Z} + \overline{X}) = \overline{y}(X+\overline{z})$$

# Example 3: Boolean Algebraic Proofs

$$\begin{array}{ll}

\overline{(X+Y)Z+XY} \\

\Rightarrow = \underline{X'(Y)Z+X(Y')} \\

\Rightarrow = \underline{Y'(X+X'Z)}

\end{array}$$

$$\begin{array}{ll}

DeMorgan's law \\

Commutative law \\

\Rightarrow Y'(X+Z)$$

### **Boolean Function Evaluation**

$$F_{1} = xy\bar{z}$$

$$F_{2} = x + \bar{y}z$$

$$F_{3} = \bar{x}\bar{y}\bar{z} + \bar{x}yz + x\bar{y}$$

$$F_{4} = x\bar{y} + \bar{x}z$$

$$F_{4} = x\bar{y} + \bar{x}z$$

$$F_{5} = x\bar{y} + \bar{x}z$$

$$F_{6} = x\bar{y} + \bar{x}z$$

$$F_{7} = x\bar{y} + \bar{x}z$$

$$F_{8} = x\bar{y} + \bar{x}z$$

$$F_{8} = x\bar{y} + \bar{x}z$$

$$F_{9} = x\bar{y} + \bar{x}z$$

| 2 | K  | y  | z  | $F_1$ | F | 72 | $F_3$ | , \ | $F_4$       |     |

|---|----|----|----|-------|---|----|-------|-----|-------------|-----|

| ( | 0  | 0  | 0  | 0     | 1 | 0  | a     | 7   | 0           | ľ   |

| ( | 0  | 0  | 1. | 0     |   | 1  | (     | ) ( | 1           |     |

|   | 0  | 1  | 0  | 1     |   | 0  |       | 0   | 0           |     |

|   | 0, | 1, | 1  |       | 0 | 0  | 1     | 1   | 1           |     |

|   | 1  | _0 | 0  |       | 0 | 1  |       | 1   | ) 1         |     |

|   | 1  | 0  | ,1 |       | 0 | 1  | 1     | I   | $\setminus$ | 1   |

|   | 1  | 1  | 1  | 0     | 1 |    | 1     | (   | )           | 0 / |

|   | 1  | 1  |    | 1     | 0 |    | 1     | \.  | 0           | 0   |

water Design Fundamentals, 4e

# **Expression Simplification**

- An application of Boolean algebra

- Simplify to contain the smallest number of <u>literals</u> (complemented and uncomplemented variables)

- Example: Simplify the following Boolean expression

- AB + A'CD + A'BD + A'CD' + ABCD

$$AB + A'CD + A'BD + A'CD' + ABCD$$

$$= AB + ABCD + A'CD + A'CD' + A'BD$$

$$= AB(1 + CD) + A'C(D + D') + A'BD$$

$$= AB. 1 + A'C. 1 + A'BD$$

$$= AB + A'C + A'BD$$

$$= AB + A'BD + A'C$$

$$= B(A + A'D) + A'C$$

$$= B(A + D) + A'C \rightarrow 5 \text{ Literals}$$

Commutative law

Levialdiners for

1 + X = 1 and X + X' = 1

X.1 = X

Commutative law

Istributive law

Simplification Theorem

### **Complementing Functions**

- Use DeMorgan's Theorem to complement a function:

- 1. Interchange AND and OR operators

- 2. Complement each constant value and literal

- Example: Complement F = (x'yz') + (xy'z')F' = (x + y' + z)(x' + y + z)

Example: Complement G = (a' + (bc))d' + e  $(a \cdot (b + c)) + d \cdot e$

$$G' = (a(b'+c')+d).e'$$

Simplify the following:

Chapter 2 -

#### Simplify the following:

•

$$F = X'YZ + X'YZ' + XZ$$

- **■** Show that F = x'y' + xy' + x'y + xy = 1

- · Solution 1: Truth Table

| x | у | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

y (x-x) +y (x+x)

Solution2: Boolean Algebra

$$x'y' + xy' + x'y + xy$$

$$= y'(x' + x) + y(x' + x)$$

$$= y'.1 + y.1$$

$$= y' + y$$

$$= 1$$

Distributive law

$$X + X' = 1$$

$$X + X' = 1$$

ogic and Computer Design Fundamentals, 4e

Chapter 2 - Part 1

50

Show that ABC + A'C' + AC' = AB + C' using Boolean algebra.

|                     |                  | *        |

|---------------------|------------------|----------|

| ABC + A'C' + AC'    |                  |          |

| =ABC+C'(A'+A)       | Distributive law | 7 4      |

| =ABC+C'.1           | X + X' = 1       | <u> </u> |

| =ABC+C'             | X. 1 = X         | ( P      |

| = (AB + C')(C + C') |                  |          |

| = (AB + C').1       | X + X' = 1       | ( A      |

| =AB+C'              | X.1 = X          |          |

ABC+C(A-A)

ABC+C

(ABC) (K-C)

(ABC) (K-C)

- Find the dual and the complement of f = wx + y'z. 0 + w'z

- Dual (f) = (w+x)(y'+z+1)(w'+z) (w+x) (y+z+1) (y+z+1)

- f' = (w' + x')(y + z' + 1)(w + z')

ic and Computer Design Fundamentals, 4e verPoint<sup>®</sup> Slides 008 Pearson Education, Inc.

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides

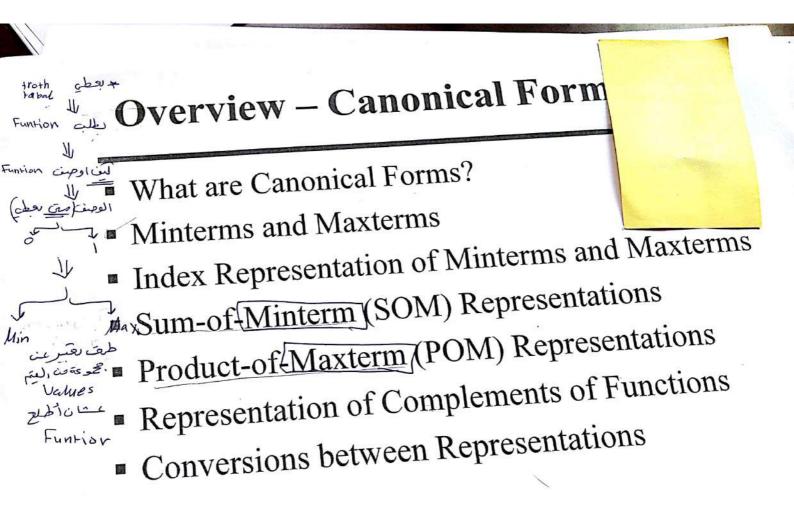

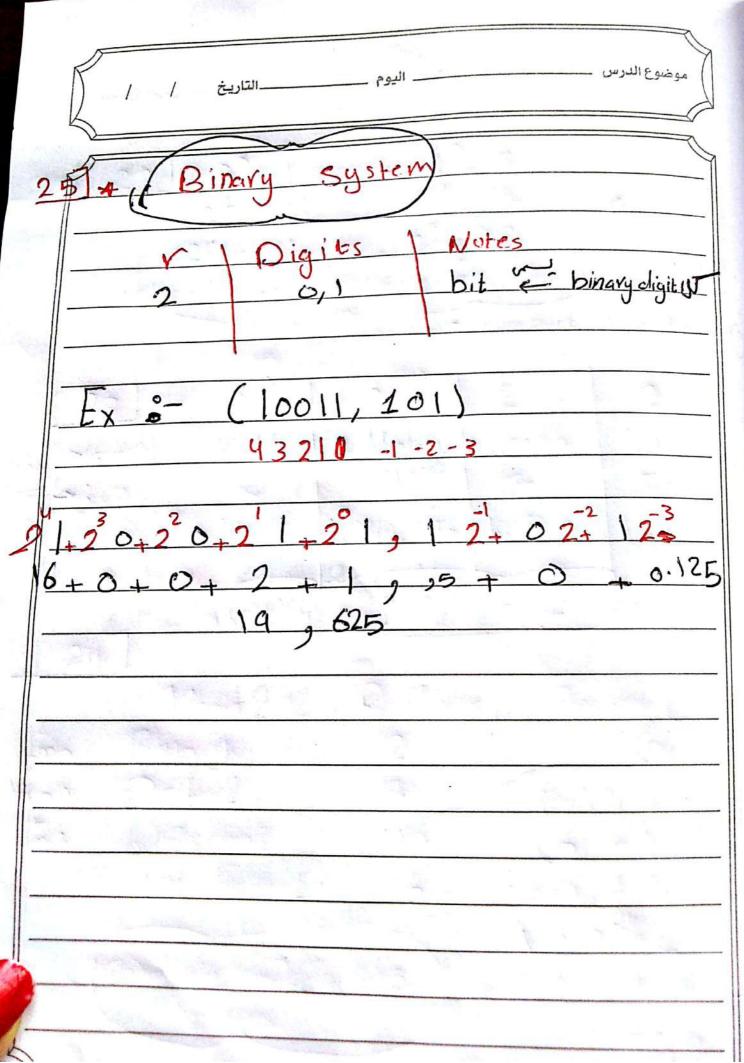

# Boolean Representation Forms

### **Canonical Forms**

- It is useful to specify Boolean functions in a form that:

- · Allows comparison for equality

- Has a correspondence to the truth tables

- Facilitates simplification

- Canonical Forms in common usage:

- Sum of Minterms (SOM)

- Product of Maxterms (POM)

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 2 - Part 1

54

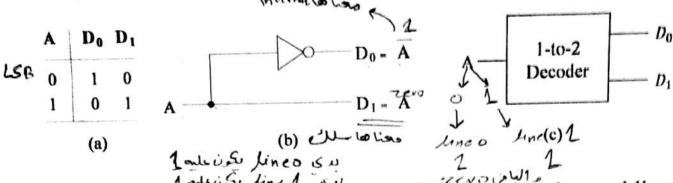

### Minterms =>

عمارة على العجدي المجلودي المجودي المجودي المجودي المجودي المجارة المحاسمة المحاسمة

- Minterms are AND terms with every variable present in either true or complemented form

- Given that each binary variable may appear normal (e.g., x) or complemented (e.g.,  $\bar{x}$ ), there are  $2^n$  minterms for n variables

- Example: Two variables (X and Y) produce  $2^2 = 4$   $2^3 = 8$  combinations:

XY (both normal)

$X\bar{Y}$  (X normal, Y complemented)

$\bar{X}Y$  (X complemented, Y normal)

$\bar{X}\bar{Y}$  (both complemented)

Thus there are four minterms of two variables

23 min → 23

Logic and Computer Design Fundamentalis, 46 PowerPoint<sup>®</sup> Stides © 2008 Pearson Education, Inc.

- Maxterms are OR terms with every variable in true or complemented form

- Given that each binary variable may appear normal (e.g., x) or complemented (e.g.,  $\bar{x}$ ), there are  $2^n$  maxterms for n variables

- Example: Two variables (X and Y) produce 2<sup>2</sup> = 4 combinations:

X + Y (both normal)

$X + \overline{Y}$  (X normal, Y complemented)

$\bar{X} + Y$  (X complemented, Y normal)

$\bar{X} + \bar{Y}$  (both complemented)

oric and Computer Design Fundamentals, 4e

Chapter 2 - Part 1

56

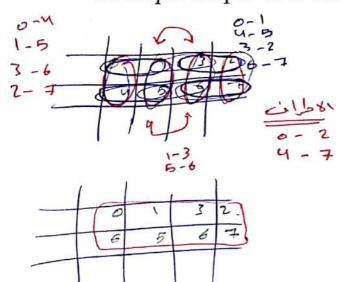

#### **Maxterms and Minterms**

| <ul><li>Examp</li></ul>              | les: Three | variable (X          | (, Y, Z) mi                     | nterms and                               | maxterms                        |

|--------------------------------------|------------|----------------------|---------------------------------|------------------------------------------|---------------------------------|

| عي معن اكاله لا يحق<br>لازع تطلح محى | Index      | X,Y,Z                | <u>Minterm</u>                  | Maxterm                                  | P00 24                          |

| رو عمله محن                          |            | X,Y,Z<br>23 = 85 Min | ( <u>m</u> )                    | (M)                                      |                                 |

| 12 38                                | 0          | 000                  | m∘ XŸZ                          | X + Y + Z                                | 16 8 4 2 1                      |

| M7 m7                                | 1          | 001                  | mı XŸZ                          | $X + Y + \bar{Z}$                        | M7= 111                         |

| الانف القدر سائن                     | 2          | 010                  | Mr. XYZ                         | $X + \overline{Y} + Z$                   | - 111                           |

| mo Mo                                | 3          | 011                  | m <sub>3</sub> $\overline{X}YZ$ | $X + \bar{Y} + \bar{Z}$                  | 1 PT = 111                      |

| 1 7 5                                | 4          | 100                  | тч $Xar{Y}ar{Z}$                | $\sqrt{X} + Y + Z$                       | र प्रेट्टा<br>१ प्रकेट प्रमुख्य |

| مريب قطم                             | 5          | 101                  | ms XŸZ                          | $\sqrt{\bar{x}} + Y + 2$                 |                                 |

| ما جهو معلون                         | 6          | 110                  | m 6 XYZ                         | $\sqrt{X} + \overline{Y} + \overline{Z}$ | Z                               |

| X, y, Z                              | 7          | 111                  | M <sub>2</sub> XYZ              | $\sqrt{X} + \overline{Y} + \overline{X}$ | $ar{Z}$                         |

The index above is important for describing which variables in the terms are true and which are complemented

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

- Minterms and maxterms are designated with a subscript

- The subscript is a number, corresponding to a binary pattern

- The bits in the pattern represent the complemented or normal state of each variable listed in a standard order

- All variables will be present in a minterm or maxterm and will be listed in the same order (usually alphabetically)

- Example: For variables a, b, c:

• Maxterms:  $(a+b+\bar{c}), (a+b+c)$

Terms: (b+a+c),  $a\bar{c}b$ , and (c+b+a) are NOT in

standard order.

Fabc

Minterms:  $a\overline{b}c$ , abc,  $\overline{a}\overline{b}c$

Terms: (a+c),  $\overline{b}c$ , and  $(\overline{a}+b)$  do not contain all variables /

اول سو ذكرنا عي تكريف [كنوى عمر Chapter 2 - Part 1

58

### Purpose of the Index

- The *index* for the minterm or maxterm, expressed as a binary number, is used to determine whether the variable is shown in the true form or complemented form

- For Minterms: المجابع المجا

- · "0" means the variable is "Complemented"

- · "1" means the variable is "Not Complemented"

- For Maxterms: → (ع)

- · "0" means the variable is "Not Complemented"

- "1" means the variable is "Complemented"

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc. Chapter 2 - Part 1

Max

## Index Example: Three Variables

| اذا عبرآ<br>عن<br>م | Index<br>(Decimal) | Index (Binary)  n = 3 Variables | Minterm (m)                           | Maxterm (M)                             |

|---------------------|--------------------|---------------------------------|---------------------------------------|-----------------------------------------|

| Ī                   | 0                  | 000                             | $m_0 \bigoplus \bar{X}\bar{Y}\bar{Z}$ | $M_0 \bigoplus X + Y + Z$               |

| ¥<br>x y 7          | 1                  | 001                             | $m_1 \in \bar{X}\bar{Y}Z$             | $M_1 \in X + Y + \bar{Z}$               |

| Sizin               | 2                  | 010                             | $m_2 = \overline{X} Y \overline{Z}$   | $M_2 = X + \overline{Y} + Z$            |

|                     | 3                  | 011                             | $m_3 = \bar{X}YZ$                     | $M_3 = X + \overline{Y} + \overline{Z}$ |

|                     |                    | 100                             | $m_4 = X\bar{Y}\bar{Z}$               | $M_4 = \bar{X} + Y + Z$                 |

| 1                   | 4                  | 101                             | $m_5 = X\bar{Y}Z$                     | $M_5 = \bar{X} + Y + \bar{Z}$           |

| <u> </u>            | 3                  | 110                             | $m_6 = XY\bar{Z}$                     | $M_6 = \bar{X} + \bar{Y} + Z$           |

| _                   | 6                  | 110                             | $m_7 = XYZ$                           | $M_7 = \bar{X} + \bar{Y} + Z$           |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

XYZ M 011 mg

Chapter 2 - Part 1

5-1919

60

## Index Example: Four Variables

| i (Decimal) | i (Binary)<br>n = 4 Variables | m <sub>i</sub>         | $\mathbf{M_i}$                          |

|-------------|-------------------------------|------------------------|-----------------------------------------|

| 0           | 0000                          | $ar{a}ar{b}ar{c}ar{d}$ | a+b+c+d                                 |

| 1           | 0001                          | ā̄b̄c̄d                | $a+b+c+\bar{d}$                         |

| 3           | 0011                          | $\bar{a}\bar{b}cd$     | $a+b+\bar{c}+\bar{d}$                   |

| 5           | 0101                          | ābēd                   | $a + \bar{b} + c + \bar{d}$             |

| 7           | 0111                          | ābcd                   | $a + \bar{b} + \bar{c} + \bar{d}$       |

| 10          | 1010                          | $aar{b}car{d}$         | $\bar{a}+b+\bar{c}+d$                   |

| 13          | 1101                          | abēd                   | $\bar{a} + \bar{b} + c + \bar{d}$       |

| 15          |                               | abcd                   | $\bar{a} + \bar{b} + \bar{c} + \bar{d}$ |

ciee 5 0 LS (9+b+C+b) 2 M 9 P Cier Design Fundamentals, 40 P M 3 P Cies Education, inc.

- Review: DeMorgan's Theorem  $\overline{x. y} = \overline{x} + \overline{y} \text{ and } \overline{x + y} = \overline{x}. \overline{y}$

- Two-variable example:

- $M_2 = \bar{x} + y$  and  $m_2 = x. \bar{y}$

- Using DeMorgan's Theorem  $\rightarrow \overline{x} + y = \overline{x} \cdot \overline{y} = x \cdot \overline{y}$

- Using DeMorgan's Theorem  $\rightarrow \overline{x. \overline{y}} = \overline{x} + \overline{\overline{y}} = \overline{x}. y$

- Thus, M<sub>2</sub> is the complement of m<sub>2</sub> and vice-versa

- Since DeMorgan's Theorem holds for *n* variables, the above holds for terms of *n* variables:

$M_{ij} = \overline{m_{ij}}$  and  $m_{ij} = \overline{M_{ij}}$

Thus, Mi is the complement of mi and vice-versa

ogic and Computer Design Fundamentals, 4e werPoint<sup>®</sup> Slides 2008 Pearson Education, Inc. Chapter 2 - Part 1

62

### **Observations**

- In the function tables:

- Each *minterm* has one and only one 1 present in the  $2^n$  terms (a minimum of 1s). All other entries are 0.

- Each maxterm has one and only one 0 present in the 2<sup>n</sup> terms All other entries are 1 (a maximum of 1s).

- We can implement any function by

ORing" the minterms corresponding to "1" entries in the function m + m table. These are called the minterms of the function.

- "ANDing" the maxterms corresponding to "0" entries in the function table. These are called the maxterms of the function. Max + Fin ispue

- This gives us two canonical forms for stating any Boolean H. H. H. function:

- Sum of Minterms (SOM)

- Product of Maxterms (POM)

Chapter 2 - Part 1

64

## **Minterm Function Example**

• Example: Find  $F_1 = m_1 + m_4 + m_7$

$$F_1 = x'y'z + xy'z' + xyz$$

| xyz | Index | $m_1 + m_4 + m_7 = F_1$                   |

|-----|-------|-------------------------------------------|

| 000 | 0     | <b>0</b> + <b>0</b> + <b>0</b> = <b>0</b> |

| 001 | 1     | 1 + 0 + 0 = 1                             |

| 010 | 2     | 0+0+0=0                                   |

| 011 | 3 、   | 0 + 0 + 0 = 0                             |

| 100 | 4     | 0+1+0=1                                   |

| 101 | 5     | 0 + 0 + 0 = 0                             |

| 110 | 6     | 0 + 0 + 0 = 0                             |

| 111 | 7     | 0 + 0 + 1 = 1                             |

my (xyz)

My (xy

65

Chapter 2 - Part 1

gic and Computer Design Fundamentals, 4 werPoint<sup>®</sup> Slides 2**006 Pearson** Education, Inc.

## **Minterm Function Example**

$F(A, B, C, D, E) = m_2 + m_9 + m_{17} + m_{23}$

$$F(A,B,C,D,E) = A'B'C'DE' + A'BC'D'E + AB'C'D'E + AB'CDE$$

ogic and Computer Design Fundamentals, 4e

## **Maxterm Function Example**

#### Example: Implement F1 in maxterms:

•

$$F_1 = M_0 \odot M_2 \odot M_3 \odot M_5 \odot M_6$$

[and]

•

$$F_1 = (x + y + z) \cdot (x + y' + z) \cdot (x + y' + z') \cdot (x' + y + z') \cdot (x' + y' + z)$$

| xyz | Index | $\mathbf{M_0}$ . $\mathbf{M_2}$ . $\mathbf{M_3}$ . $\mathbf{M_5}$ . $\mathbf{M_6} = \mathbf{F_1}$ |

|-----|-------|---------------------------------------------------------------------------------------------------|

| 000 | 0     | 0.1.1.1.1=0                                                                                       |

| 001 | 1     | 1.1.1.1.1=1                                                                                       |

| 010 | 2     | 1.0.1.1.1=0                                                                                       |

| 011 | 3     | 1.1.0.1.1=0                                                                                       |

| 100 | 4     | 1.1.1.1.1=1                                                                                       |

| 101 | 5     | 1.1.1.0.1=0                                                                                       |

| 110 | 6     | 1.1.1.0=0                                                                                         |

| 111 | 7     | 1.1.1.1.1=1                                                                                       |

Logic and Computer Design Fundamentals, 4e

PowerPoint® Slides

## Maxterm Function Example

$$F(A,B,C,D) = M_3 . M_8 . M_{11} . M_{14}$$

F(A, B, C, D)

$$= (A + B + C' + D') \cdot (A' + B + C + D) \cdot (A' + B + C' + D') \cdot (A' + B' + C' + D)$$

$$M_3$$

$A+B+C+D$

$M_8$

$A+B+C+D$

$M_1$

$M_1$

$A+B+C+D$

$M_1$

$M$

ا صبح سي بسيكو ت Funtion ودينون دشونا فغض ودينون مارنا رتص مثار ا

Iny Boolean function can be expressed as a Sum of Minterms (SOM):

- For the function table, the minterms used are the terms corresponding to the 1's

- For expressions, expand all terms first to explicitly list all minterms. Do this by "ANDing" any term missing a variable v with a term  $(v + \bar{v})$

Example: Implement  $f = \overline{x} \bar{y}$  as a SOM?  $\overline{x}(x, y, z)$

- 2. Distributive law  $\rightarrow f = xy + x\bar{y} + \bar{x}\bar{y}$

- 3. Express as SOM  $\rightarrow f = m_3 + m_2 + m_0 = m_0 + m_2 + m_3$   $\times y \quad m_z$

Ký mz

ogic and Computer Design Fundamentals, 4e lowerPoint® Slides

2008 Pearson Education, Inc.

Chapter 2 - Part 1

72

### **Another SOM Example**

- Example:  $F = A + \overline{B}C \longrightarrow A(B+\overline{B})(c+\overline{c}) + Bc(A+\overline{A})$

- There are three variables: A, B, and C which we take to be the standard order

- Expanding the terms with missing variables:

•

$$F = A(B + \overline{B})(C + \overline{C}) + (A + \overline{A})\overline{B}C$$

Distributive law:

•

$$F = ABC + A\overline{B}C + AB\overline{C} + A\overline{B}\overline{C} + A\overline{B}C + \overline{A}\overline{B}C$$

Collect terms (removing all but one of duplicate terms):

•

$$F = ABC + AB\bar{C} + A\bar{B}C + A\bar{B}\bar{C} + \bar{A}\bar{B}C$$

Express as SOM:

•

$$F = m_7 + m_6 + m_5 + m_4 + m_1$$

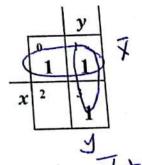

#### **Shorthand SOM Form**

■ From the previous example, we started with:

$$F = A + \overline{B}C$$

- We ended up with:

- $F = m_1 + m_4 + m_5 + m_6 + m_7$

- This can be denoted in the formal shorthand:

•

$$F(A, B, C) = \sum_{m} (1,4,5,6,7)$$

Note that we explicitly show the standard variables in order and drop the "m" designators.

#### **Canonical Product of Maxterms**

- Any Boolean Function can be expressed as a Product of Maxterms (POM):

- For the function table, the maxterms used are the terms corresponding to the 0's

- For an expression, expand all terms first to explicitly list all maxterms. Do this by first applying the second distributive law, "ORing" terms missing variable v with  $(v \cdot \bar{v})$  and then applying the distributive law again

- Example: Convert  $f(x, y, z) \neq x + \bar{x}\bar{y}$  to POM?

- Distributive law  $\rightarrow f = (x + \overline{x}) \cdot (x + \overline{y}) = x + \overline{y}$

- ORing with missing variable (z)  $\rightarrow f = x + \bar{y} + z \cdot \bar{z}$

- Distributive law  $\rightarrow f = (x + \bar{y} + z) \cdot (x + \bar{y} + \bar{z})^8$

- Express as POS  $\rightarrow f = M_2 . M_3$

## **Another POM Example**

- Convert f(A, B, C) = AC' + BC + A'B' to POM?

- $Us \notin x + yz = (x + y) \cdot (x + z)$ , assuming x = AC' + BC and y = A' and z = B'

- $f(A,B,C) = (AC' + BC + A') \cdot (AC' + BC + B')$

- Use Simplification theorem to get:

- $f(A,B,C) = (BC + A' + C') \cdot (AC' + B' + C)$  Use Simplification theorem again to get:

- $f(A,B,C) = (A'+B+C') \cdot (A+B'+C) = M_5 \cdot M_2$

- $f(A, B, C) = M_2 \cdot M_5 = \prod_M (2,5) \rightarrow Shorthand POM$ form

## **Function Complements**

- The complement of a function expressed as a sum of minterms is constructed by selecting the minterms missing in the sum-of-minterms canonical forms.

- Alternatively, the complement of a function expressed by a sum of minterms form is simply the Product of Maxterms with the same indices.

- Example: Given  $F(x,y,z) = \sum_{m} (1,3,5,7)$ , find complement F as SOM and POM?

- $F(x, y, z) = \sum_{m=0}^{\infty} (0,2,4,6)$

- $F(x, y, z) = \prod_{M} (1,3,5,7)$

Computer Design Fundamentals, 4ent<sup>®</sup> Slides

Chanter 2 Dont 1

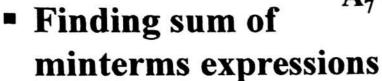

#### **Conversion Between Forms**

- To convert between sum-of-minterms and product-of-maxterms form (or vice-versa) we follow these steps:

- Find the function complement by swapping terms in the list with terms not in the list.

- · Change from products to sums, or vice versa.

- **Example:** Given F as before:  $F(x, y, z) = \sum_{m} (1,3,5,7)$

- Form the Complement:  $\overline{F}(x, y, z) = \sum_{m} (0,2,4,6)$

- Then use the other form with the same indices this forms complement again, giving the other form of the original function:

$$F(x,y,z) = \prod_{M} (0,2,4,6)$$

$$F(x/y/z) = \prod_{M} (1/3/5/7)$$

Chapter 2 - Par

and Computer Design Fundamentals, 4e

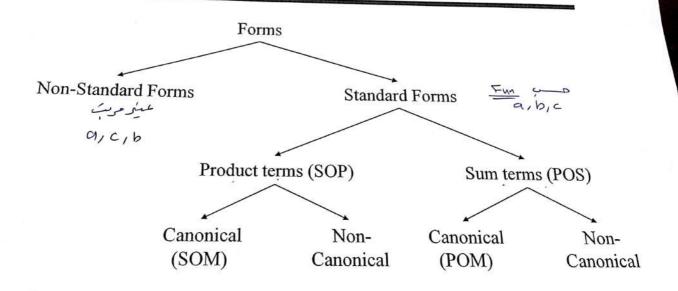

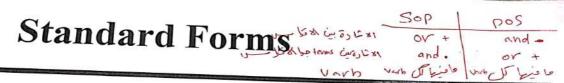

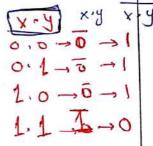

- Standard Sum-of-Products (SOP) form: equations are written as an OR of AND terms

- Standard Product-of-Sums (POS) form: equations are written as an AND of OR terms

- Examples:

- SOP:  $ABC + \overline{ABC} + \overline{B}$

- POS:  $(\underline{A} + \underline{B})$ .  $(A + \overline{B} + \overline{C})$ .

- (AB+C)(A+C) (AC+AB)

- $AB\bar{C} + AC(A+B)$

وي مالة هذه لا حوم م

\* (AB+C) (A+C)

(A+C)(B+C) (A+C)

prof pos

\* ABC + AC (A+B) (ABC) + (ACA)+(ACB) \$ SOP

## Standard Sum-of-Products (SOP)

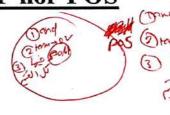

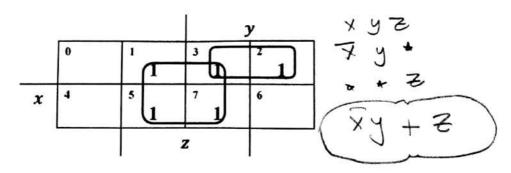

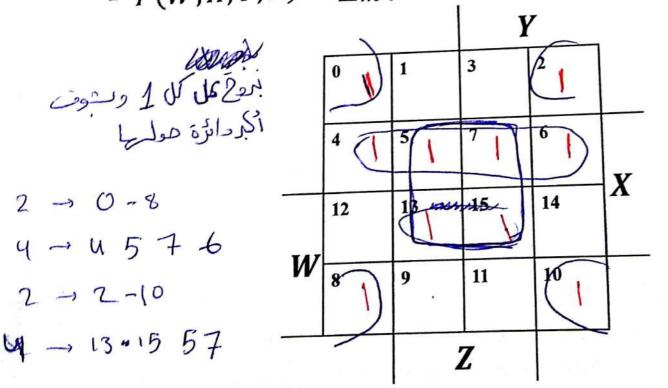

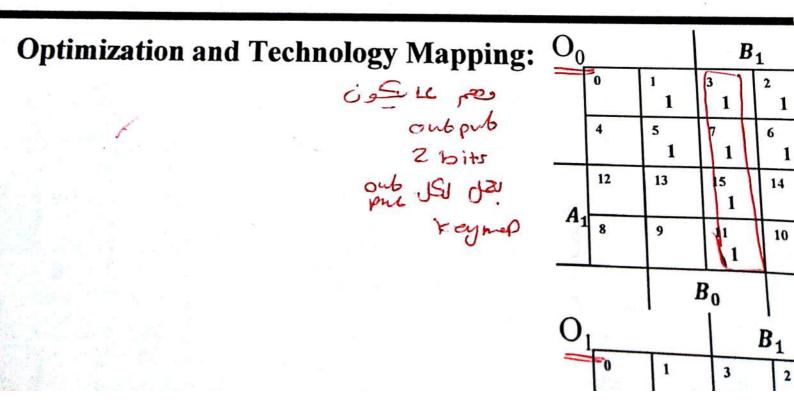

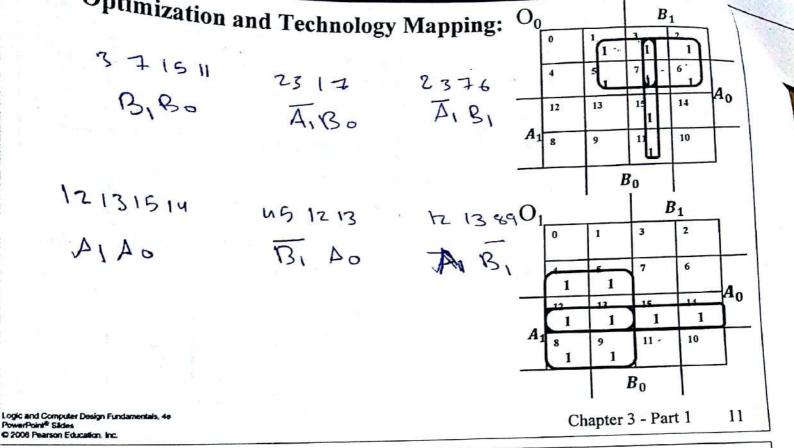

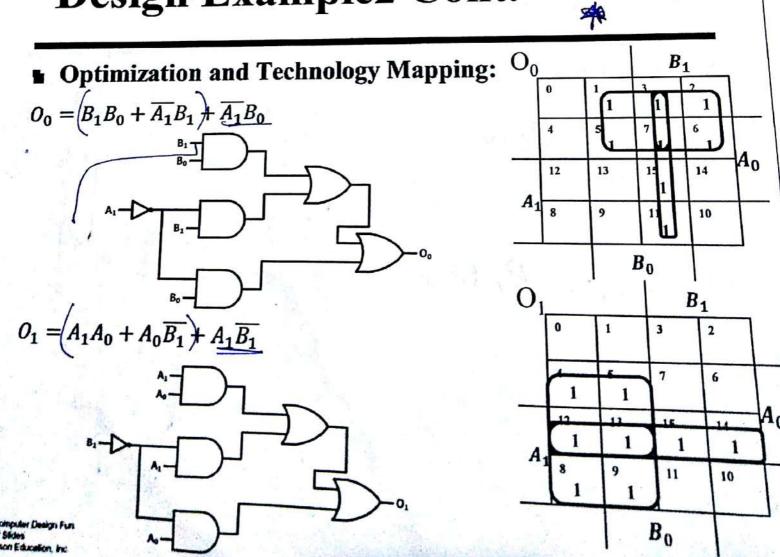

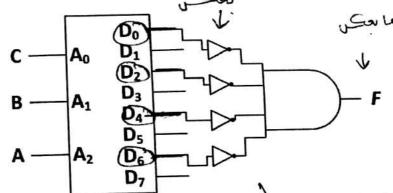

- A Simplification Example:  $F(A, B, C) = \sum_{m} (1,4,5,6,7)$

- Writing the minterm expression:

- F(A,B,C) = A'B'C + AB'C' + AB'C + ABC' + ABC

- Simplifying using boolean Algebra:

Simplified F contains 3 literals compared to 15 in minterm F

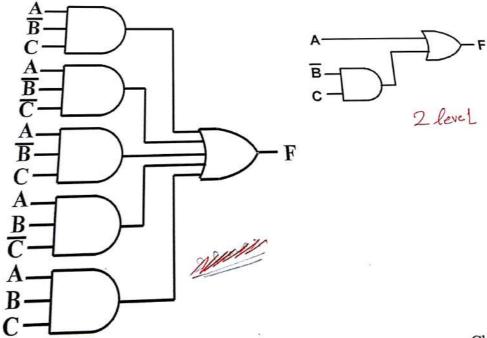

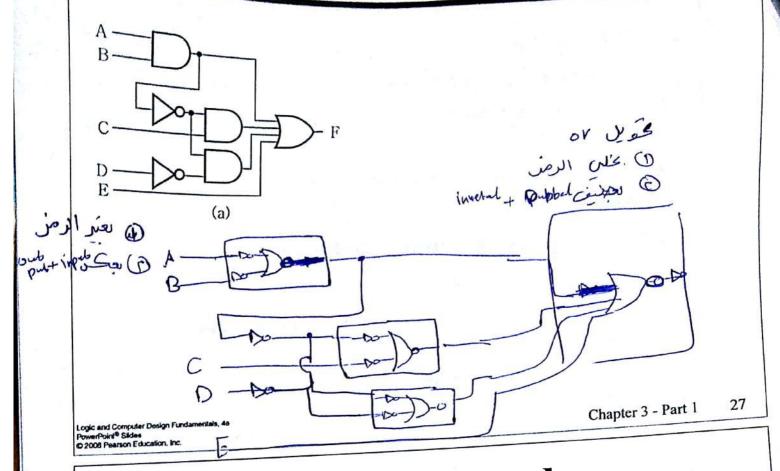

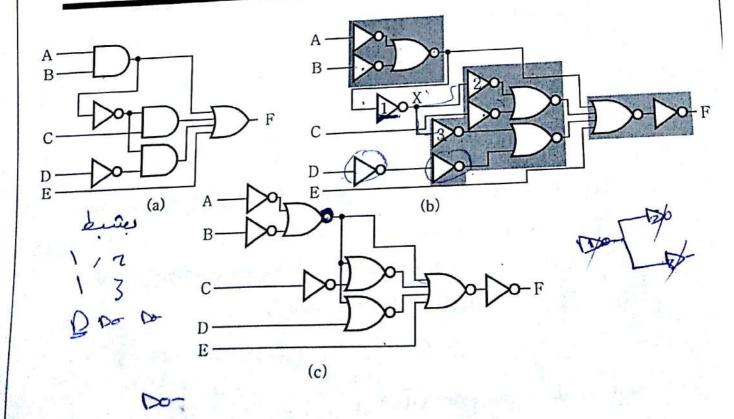

# AND/OR Two-level Implementation of SOP Expression

■ The two implementations for F are shown below — it is quite apparent which is simpler!

ogic and Computer Design Fundamentals, 48 PowerPoint® Stides

garde the Karen earimal Binra Oct ras Herrals \* بكون بالمسمة الرفتم على ع (46), -> (0110) 2

Scanned by CamScanner

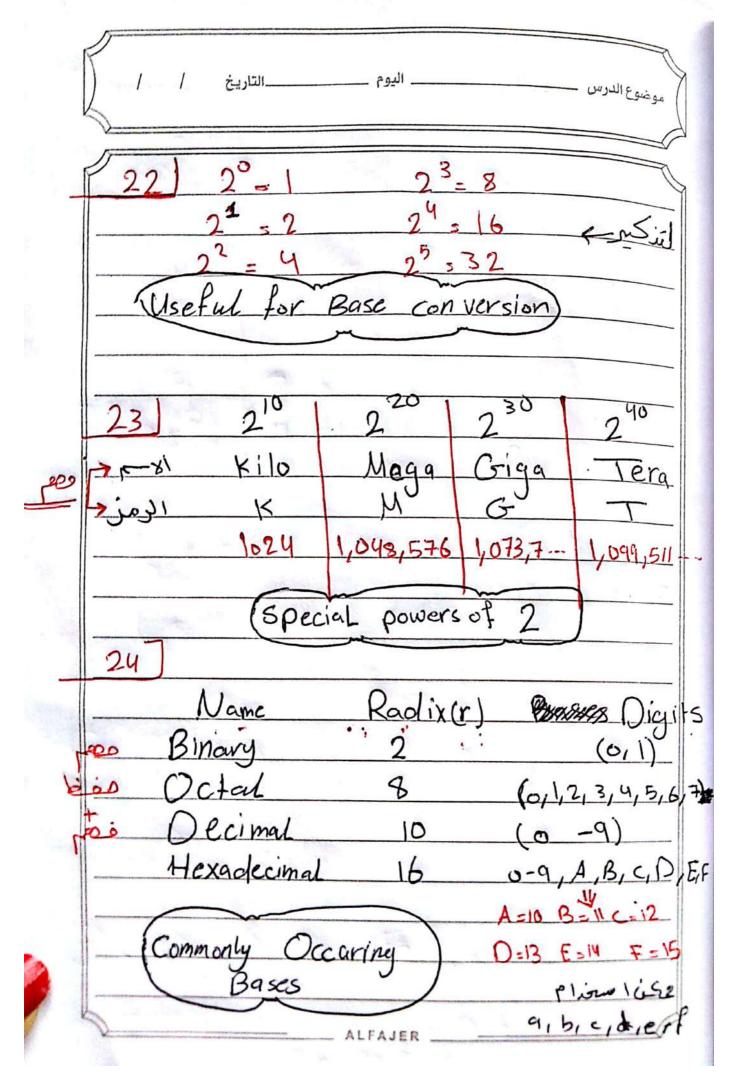

Cooling in Cooling 1 Eur & Ear & Phi shie \* 215 (21) P32 coding J83 612 c mas # ص عدد الخانات Decimal  $\frac{10^2}{(r)}$ 82 , 6U octal Dinary ای موهد رعندك

| ويفوع الدوم التاريخ / /                                |

|--------------------------------------------------------|

| 49 Oct > Who sure I pli sur 'slip<br>ex) ex) 8" >, 365 |

| N = 1                                                  |

| ns 5122 512) 356                                       |

| diplosición de log r = log m                           |

| $N = \log_{r} m$                                       |

|                                                        |

| n = log, m                                             |

| ر ا نی از ا کی از ا کی ا                               |

| [3.00001] 3.9999 J                                     |

| ALFAJER                                                |

#### Overview

- Part 1 Gate Circuits and Boolean Equations

- · Binary Logic and Gates

- Boolean Algebra

- Standard Forms

- Part 2 Circuit Optimization

- · Two-Level Optimization

- · Map Manipulation

- Part 3 Additional Gates and Circuits

- · Other Gate Types

- · Exclusive-OR Operator and Gates

- High-Impedance Outputs

SOSas

Chapter 2 - Part 2

3

Logic and Computer Design Fundamentals, 4a PowerPoint® Sides. © 2008 Pageson Education, Inc.

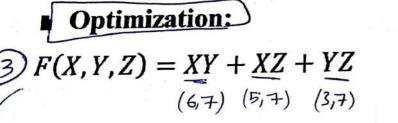

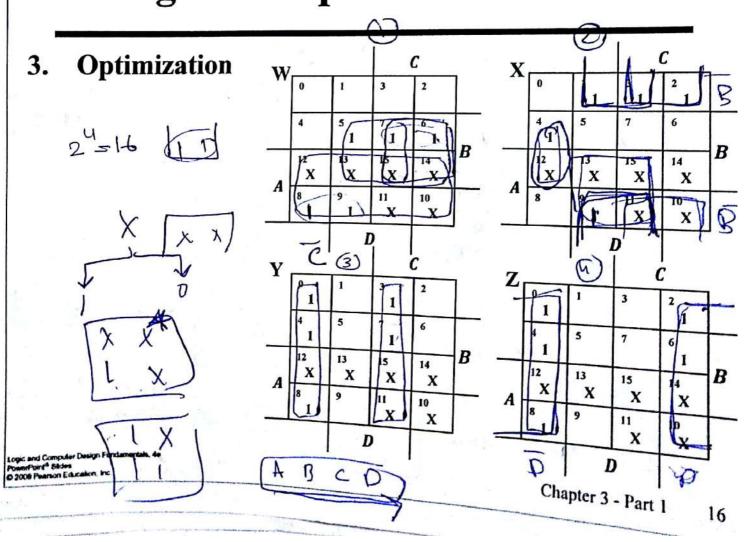

## Circuit Optimization

- Goal: To obtain the simplest implementation for a given function

- Optimization is a more formal approach to simplification that is performed using a specific procedure or algorithm

- Optimization requires a cost criterion to measure the simplicity of a circuit

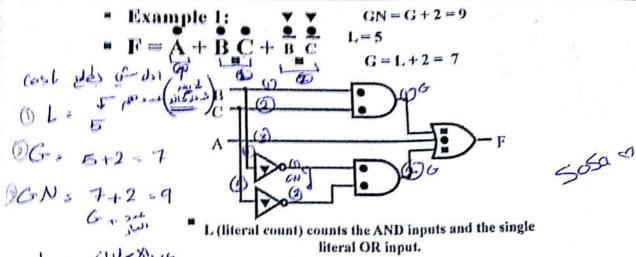

- Distinct cost criteria we will use: Lost

Literal cost (L)

Gate input cost (G)

Gate input cost with NOTs (GN)

and Computer Design Functionentals, 4e Puint States Fearson Education, Inc

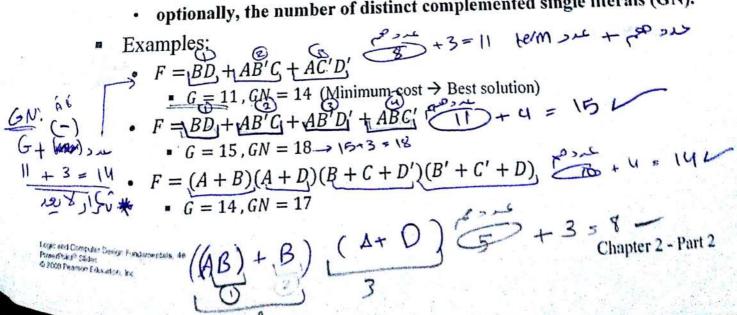

## Literal Cost (L)

literal of number Literal the cost (L): expression Boolean appearances in a diagram corresponding to the logic circuit م العدلم الما الم المعدود العدود

Examples:

•

$$F = \overrightarrow{BD} + \overrightarrow{AB'C} + \overrightarrow{AC'D'} \rightarrow \$$$

■ L = 8 (Minimum cost  $\rightarrow$  Best solution)

•

$$F = \overrightarrow{BD} + \overrightarrow{AB'C} + \overrightarrow{AB'D'} + \overrightarrow{ABC'}$$

•

$$F = (A + B)(A + D)(B + C + D')(B' + C' + D)$$

•  $L = 10$

Logic and Computer Design Fundamentals, 4e PowerPoint® Skides © 2008 Pearson Education, Inc.

Chapter 2 - Part 2

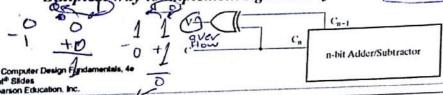

## Gate Input Cost (G)

- Gate input cost (G): the number of inputs to the gates in the implementation corresponding exactly to the given equation or equations. (G: inverters not counted, GN: inverters counted)

- For SOP and POS equations, it can be found from the equation(s) by finding the sum of:

- All literal appearances

- The number of terms excluding single literal terms,(G) and

- optionally, the number of distinct complemented single literals (GN).

### Cost Criteria (continued)

لا الحالات المحالات المحالات

GN(gate input count with NOTs) adds the inverter (nputs

Chapter 2 - Part 2

7

### Cost Criteria (continued)

- Example 2:

- F = (A, B, C, D) = (ABC + D').C'• L = 5

- G = 5 + 2 = 7

- GN = 7 + 2 = 9• GN = 7 + 2 = 9• GN = 7 + 2 = 9

1,5 GNS1

Promote par Chiefs Si Men Proposit I de monte de Chapter 2 - Part 2

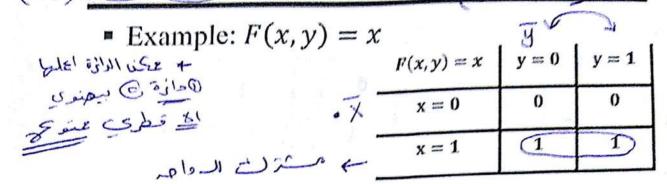

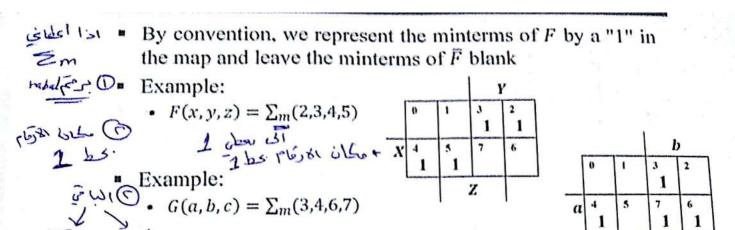

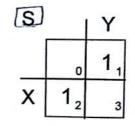

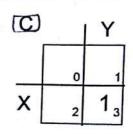

### K-Map Function Representation

For function F(x, y), the two adjacent cells containing 1's can be combined using the Minimization Theorem:

Topic and Consider Design Fundamentals, de Physician Species

$$F(x,y) = x\bar{y} + xy = (\bar{x})$$

Logic and Consider Design Fundamentals, de Physician Species  $X$  ( $\bar{y} + y$ )

Chapter 2 - Part 2 15

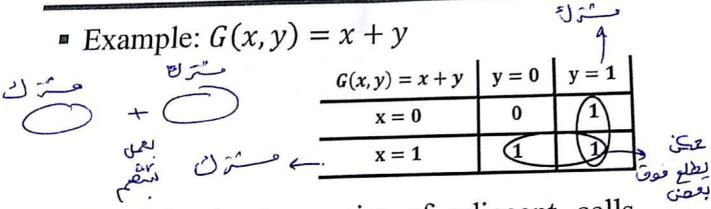

### K-Map Function Representation

For G(x, y), two pairs of adjacent cells containing 1's can be combined using the Minimization Theorem:

$$G(x,y) = (x\bar{y} + xy) + (\bar{x}y + xy)$$

$$G(x,y) = x + y$$

### K-Map and Truth Tables

- The K-Map is just a different form of the truth table

- Example: Two variable function

- We choose a,b,c and d from the set  $\{0,1\}$  to implement a particular function, F(x,y)

| Input Values (x, y) | $\mathbf{F}(\mathbf{x}, \mathbf{y})$ |

|---------------------|--------------------------------------|

| 0 0                 | а                                    |

| 01                  | b                                    |

| 10                  | c                                    |

| 11                  | d                                    |

طبعة توزيع المملط في لخ

|                  | <u> </u> |                         |

|------------------|----------|-------------------------|

|                  | y = 0    | y = 1                   |

| $\sqrt{x} = 0$   | a mo     | <b>b</b> m <sub>1</sub> |

| $\mathbf{x} = 1$ | c m 2    | d m3                    |

**Truth Table**

K-Map

Logic and Computer Decays Fundamentals, 4e Complement Status G 2008 Pearson Education, Inc.

Chapter 2 - Part 2

$$F = \bar{x}y + \bar{x}\bar{y}$$

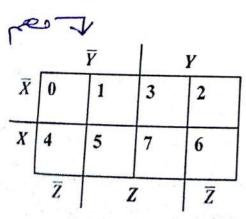

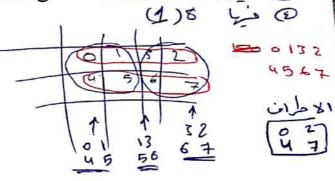

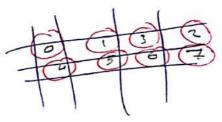

### Three Variable Maps

A three-variable K-man:

|    |                | السينه  |       | yz = 00     | yz = 01 | yz = 11 | yz = 10 |

|----|----------------|---------|-------|-------------|---------|---------|---------|

| mo | m              | (m2) m2 | x = 0 | $\dot{m}_0$ | $m_1$   | $m_3$   | $m_2$   |

| my | m <sub>6</sub> | m m     | x = 1 | $m_4$       | $m_5$   | $m_7$   | $m_6$   |

Where each minterm corresponds to the product terms:

|   | Ċ  | 9   |                | 4   | <b>.</b> |

|---|----|-----|----------------|-----|----------|

| V | mo | mi  | m <sub>3</sub> | m2  | 111      |

| 7 | my | ms  | ma             | m 6 |          |

| ^ | 2  | 1-2 |                | 豆   |          |

|   |       |                         | U=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | S.          | 5)                |

|---|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|

|   |       | yz = 00                 | THE RESERVE OF THE PARTY OF THE | yz = 11     | yz = 10           |

| X | x = 0 | $\bar{x}\bar{y}\bar{z}$ | $\bar{x}\bar{y}z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\bar{x}yz$ | $\bar{x}y\bar{z}$ |

| X | x = 1 | $x\bar{y}\bar{z}$       | $x\bar{y}z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xyz         | $xy\bar{z}$       |

| • |       | 250                     | 一元:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1          | 520               |

Note that if the binary value for an index differs in one bit position, the minterms are adjacent on the K-Map

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc.

Chapter 2 - Part 2

17

### Alternative Map Labeling

- Map use largely involves:

- · Entering values into the map, and

- · Reading off product terms from the map

- Alternate labelings are useful:

olderster, by

| YZ   | 00 | 01 | 11 | 10       |

|------|----|----|----|----------|

| 0    | 0  | 1  | 3  | 2        |

| x √1 | 4  | 5  | 7  | 6        |

| 14 1 | 2  |    |    | <u> </u> |

Learn the locations of the 8 indices based on the variable order shown (X, most significant and Z, least significant) on the map boundaries

Logic and Computer Design Fundamentals, 4a PowerPoint\* Stidies © 2009 Pearson Education, loc

Chapter 2 - Part 2

19

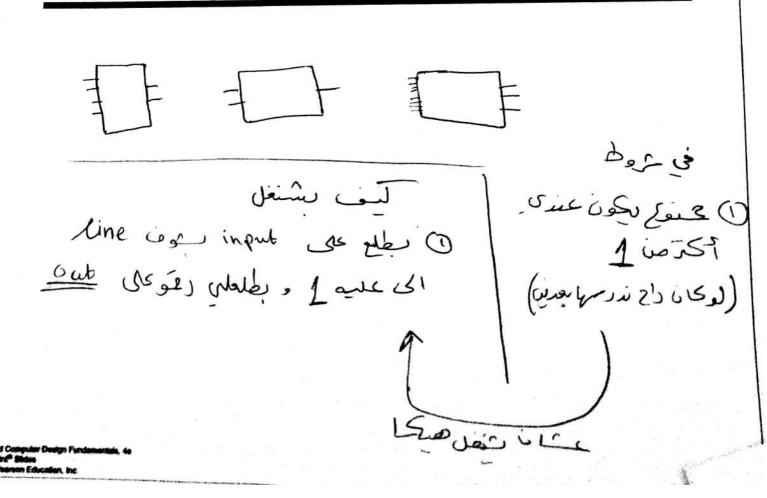

Steps for using K-Maps to Simplify Boolean **Functions**

Enter the function on the K-Map

Function can be given in truth table, shorthand notation, SOP,...etc

Example:  $F(x,y) = \bar{x} + xy$

|        |   | ***        | 10 4 1  | •  |

|--------|---|------------|---------|----|

| F(x,y) | = | $\sum_{m}$ | (0,1,3) | S) |

| x | У | $\mathbf{F}(\mathbf{x},\mathbf{y})$ |

|---|---|-------------------------------------|

| 0 | 0 | 1                                   |

| 0 | 1 | 1                                   |

| 1 | 0 | 0                                   |

| 1 | 1 | 1                                   |

Combining squares for simplification

Rectangles that include power of 2 squares {1, 2, 4, 8, ...}

Goal: Fewest rectangles that cover all 1's → as large as possible

Determine if any rectangle is not needed

20

Lugic and Computer Design Fundamentals, 44 Powerfour Pades © 2009 Pearson Education, Inc.

Scanned by CamScanner

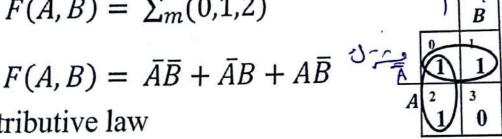

### Example: Combining Squares

• Example:  $F(A, B) = \sum_{m} (0,1,2)$

- Using Distributive law

- $F(A,B) = \bar{A} + A\bar{B}$

- Using simplification theorem

•

$$F(A,B) = \widehat{A} + \widehat{B}$$

Thus, every two adjacent terms that form a 2×1 rectangle correspond to a product term with one variable

#### Three-Variable Maps

مارات العالي صنيا (1) واحد 0 - 7

■ Example shapes of 2-cell rectangles: <

Chapter 2 - Part 2

25

### Three-Variable Maps

Example shapes of 2-cell rectangles:

عاً الشوف المائة ك سيائ سريت حب المعثم ل بعائد معرفة بالمعمران بعائد بعائد بالمعمران بعائد بعائد بالمعمران

- Read-off the product terms for the rectangles shown:

- $Rect(0,1) = \bar{X}\bar{Y}$

- K X X

- $Rect(0,2) = \bar{X}\bar{Z}$

- XXX

- Rect(3,7) = YZ

- # 7 7

Example shapes of 4-cell Rectangles:

- Read off the product terms for the rectangle shown:

- $Rect(4,5,6,7) = X \times *$

Chapter 2 - Pa

- K-maps can be used to simplify Boolean functions by systematic methods. Terms are selected to cover the "1s" in the map.

- Example: Simplify  $F(x, y, z) = \sum_{m} (1,2,3,5,7)$

$$F(x, y, z) = z + \bar{x}y$$

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Stides © 2008 Pearson Education, Inc.

Chapter 2 - Part 2

29

### Three-Variable Map Simplification

• Use a K-map to find an optimum SOP equation for  $F(X, Y, Z) = \sum_{m} (0,1,2,4,6,7)$

### Three-Variable Map Simplification

Use a K-map to find an optimum SOP equation for  $F(X, Y, Z) = \sum_{m} (0,1,2,4,6,7)$

$F(X,Y,Z) = \bar{Z} + \bar{X}\bar{Y} + XY$

Logic and Computer Design Fundamentals, de PowerPoint® States © 2008 Pearson Education, Inc.

© 2008 Perenio Education, Ira

Chapter 2 - Part 2

31

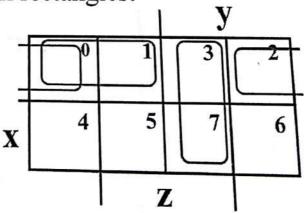

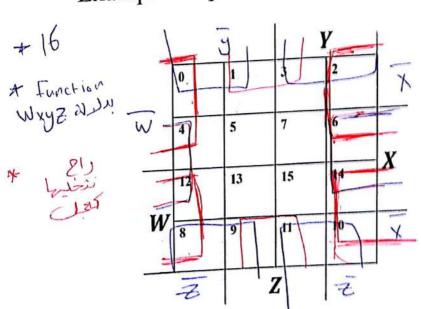

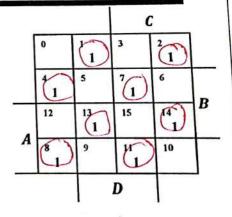

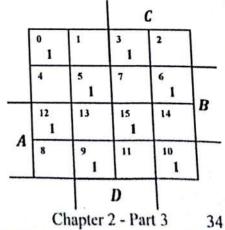

### Four Variable Maps

Map and location of minterms F(W,X,Y,Z): 6 X13 15 2 yumb 1 = 51, 2 Logic and Computer Outsign Fundamentals, by 3 Vary b - 2 3513

Scanned by CamScanner

Chapter 2 - Part 2

### Four Variable Terms

- Four variable maps can have rectangles corresponding to:

- A single 1:

- 4 variables (i.e. Minterm)

- Two 1's:

- 3 variables

- · Four I's:

- 2 variables

- Eight 1's:

- 1 variable

- · Sixteen 1's:

- zero variables (function of all ones)

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Sides © 2008 Pourson Education, Inc. Chapter 2 - Part 2

33

### Four-Variable Maps

Example shapes of 4-cell rectangles:

04-26 412-64 128-1010 and 01-21 13-011 32-110 02-810

Chapter 2 - Part 2

34

### Example shapes of 4-cell rectangles:

Logic and Computer Design Psychimerists, & Frankfishi<sup>®</sup> Bibbes is now Peacent Estandon, Inc. Chapter 2 - Part 2

35

### Four-Variable Maps

### Example shapes of 8-cell rectangles:

Media 10 11 12 18 - 26/4/0

I with = E

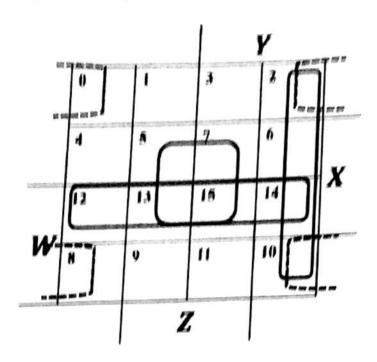

## Four-Variable Map Simplification

$F(W,X,Y,Z) = \sum_{m} (0,2,4,5,6,7,8,10,13,15)$

Logic and Computer Design Fundamentals, 4e PowerPoint® Sildes © 2006 Pearson Education, Inc.

Chapter 2 - Part 2

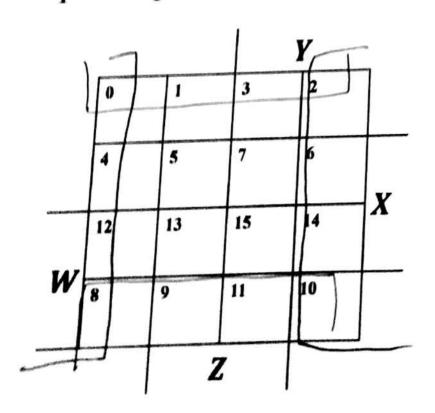

### Four-Variable Map Simplification

•  $F(W,X,Y,Z) = \sum_{m} (3,4,5,7,9,13,14,15)$

$F(W,X,Y,Z) = \overline{W}YZ + \overline{W}X\overline{Y} + WXY + W\overline{Y}Z$ Logic and Computer Design Fundamentals, 40

PowerFully States

0 2008 Phanson Edyfalor, Hz. 52 Cl U + Essential U - Chapter 2 - Part 2

41

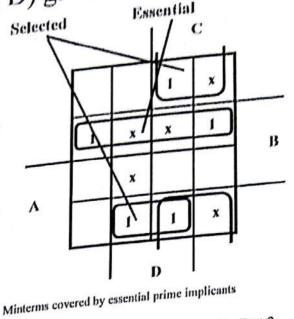

### **Systematic Simplification**

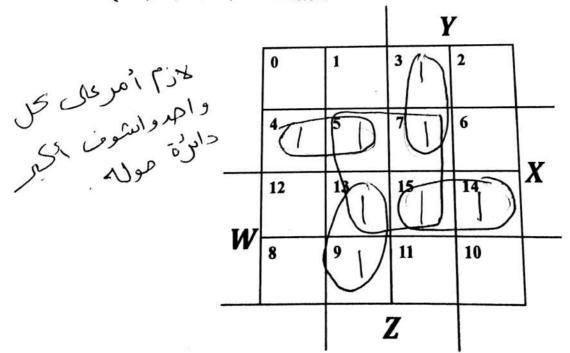

- Prime Implicant: is a product term obtained by combining the maximum possible number of adjacent squares in the map into a rectangle with the number of squares a power of 2

- A prime implicant is called an <u>Essential Prime Implicant</u>

if it is the <u>only</u> prime implicant that covers (includes) one

or more minterms

- Prime Implicants and Essential Prime Implicants can be determined by inspection of a K-Map

- A set of prime implicants "covers all minterms" if, for each minterm of the function, at least one prime implicant in the set of prime implicants includes the minterm

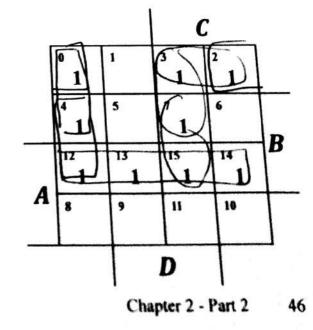

### Four-Variable Map Simplification

•

$$F(W,X,Y,Z) = \sum_{m} (0,2,4,5,6,7,8,10,13,15)$$

$$F(W,X,Y,Z) = XZ + \bar{X}\bar{Z} + \bar{W}X$$

Logic and Computer Design Fundamentals, 4s ProverPoint<sup>®</sup> Bildes © 2009 Pearson Education, Inc. Chapter 2 - Part 2

39

### Four-Variable Map Simplification

•  $F(W,X,Y,Z) = \sum_{m} (3,4,5,7,9,13,14,15)$

$F(W,X,Y,Z) = \overline{W}YZ + \overline{W}X\overline{Y} + WXY + W\overline{Y}Z$

ogic and Computer Design Fundamentals, 4e used obtain 88des

Chapter 2 - Part 2

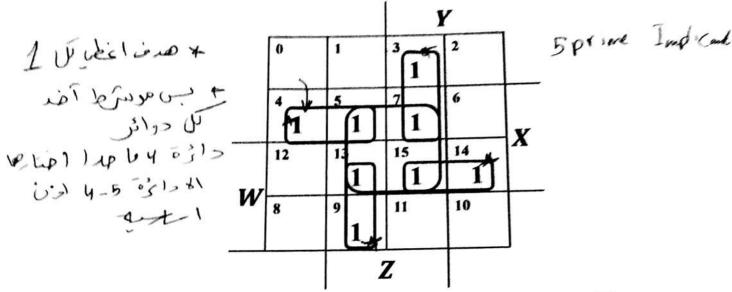

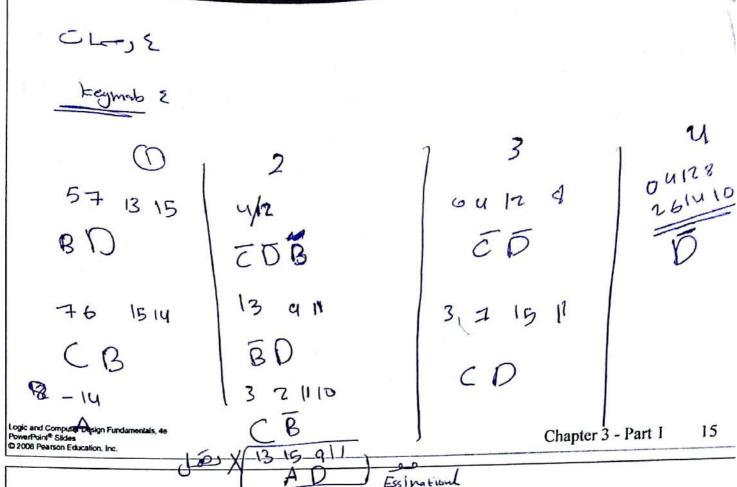

### **Prime Implicant Practice**

Find all prime implicants for:

$$F(A,B,C,D) = \sum_{m} (0,2,3,8,9,10,11,12,13,14,15)$$

Logic and Computer Design Fundamentals, 4e PowerPoint® Stides © 2008 Peanson Education, Inc. Chapter 2 - Part 2

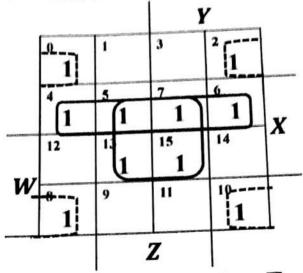

### **Another Example**

Find all prime implicants for:

$$G(A, B, C, D) = \sum_{m} (0,2,3,4,7,12,13,14,15)$$

- Hint: There are seven prime implicants!

- Prime Implicants:

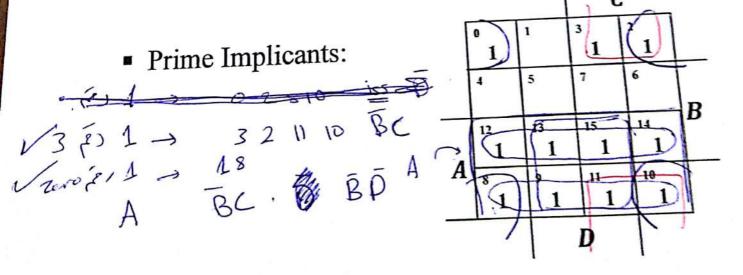

### Selection Rule Example

tundamentals, 4e

Chapter 2 - Part 2

### Selection Rule Example

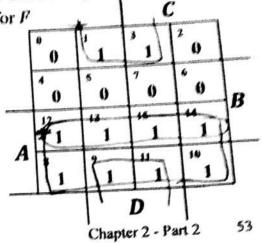

Find the optimum POS solution for:

$$F(A,B,C,D) = \sum_{m} (1,3,9,11,12,13,14,15)$$

- Solution:

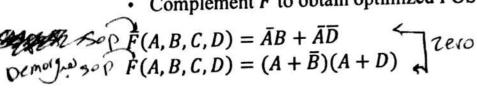

- Find optimized SOP for \(\bar{F}\) by combining 0's in K-Map of \(\bar{F}\)

C • Complement  $\overline{F}$  to obtain optimized POS for F0 1 1 ( o 0 0 0 B 13 15 4,5,7,6 -A B 1 1 1 1 F = (AB) + (BD)

Product of Sums Example 51

Find the optimum POS solution for:

$$F(A,B,C,D) = \sum_{m} (1,3,9,11,12,13,14,15)$$

- Solution:

- Find optimized SOP for  $\overline{F}$  by combining 0's in K-Map of F

| • Complement $\overline{F}$ to obtain optim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nized POS for F |         | C         |         |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-----------|---------|----|

| SOPF grow vero vero v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | 1<br>1  | 1         | 0       |    |

| 0,2,8,10 - BD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40              | 5       | 7         | 0       | R  |

| 4,5,4,6 → A B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 12            | 13<br>1 | 15<br>1   | 14<br>1 |    |

| F = (AB) + (BD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A 8 0           | 9       | 11<br>1   | 0       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |         | D         | 1       |    |

| Logic and Computer Design Fundamentals, 4e PowerPoint® Stokes  2 445 Physican Computer Comput | (1 T) (A        | Chapte  | er 2 - Pa | rt 2    | 51 |

Product of Sums Example

PUS

F group 4 -> Sop-F -> pos

1 Viso o's's si

ablish pos F -> sop F -> group das

ablifipos F - SOPF - group var,

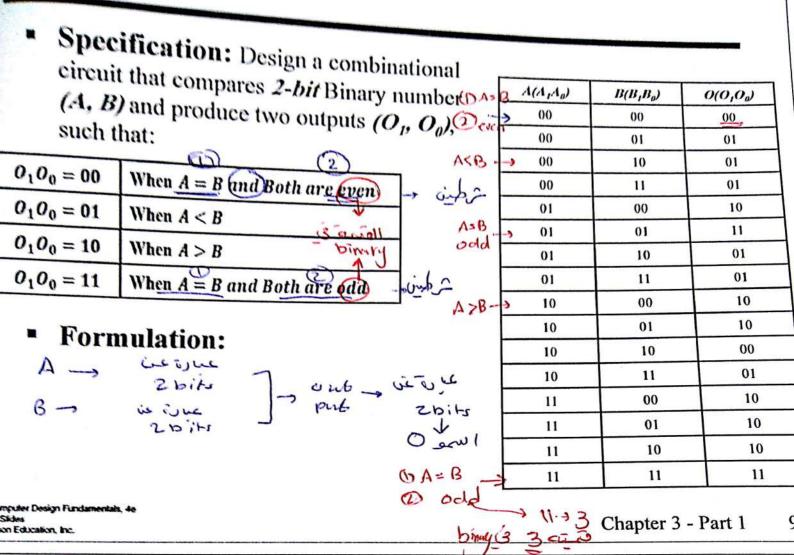

#### Example

Find the optimum POS and SOP solution for:

$$F(A,B,C,D) = \prod_{M} (0,2,4,5,6,7)$$

$$N = \{1,2,4,5,6,7\}$$

- POS solution (Red): 1 POS solution (Red): 1 POS solution

- Find optimized SOP for  $\overline{F}$  by combining 0's in K-Map of F

Complement \( \bar{F} \) to obtain optimized POS for \( F \)

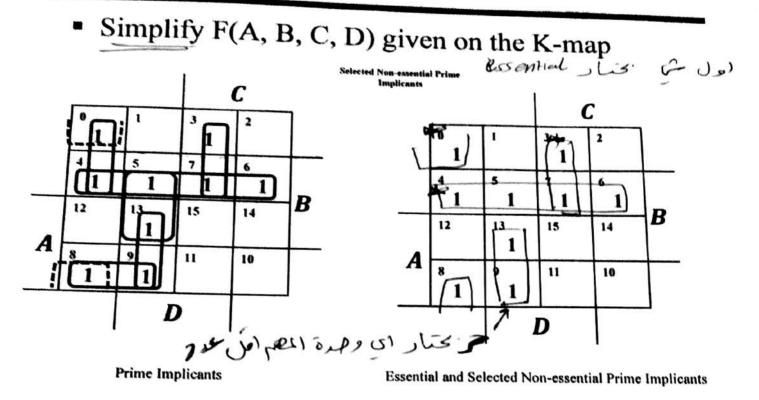

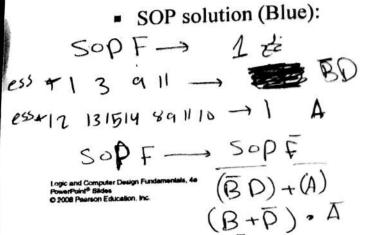

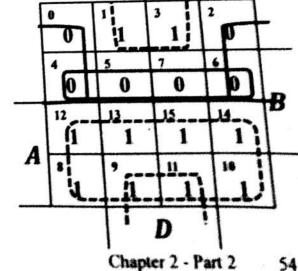

### Example

Find the optimum POS and SOP solution for:

$$F(A, B, C, D) = \prod_{M} (0, 2, 4, 5, 6, 7)$$

- POS solution (Red):

- Find optimized SOP for  $\overline{F}$  by combining 0's in K-Map of F

• Complement  $\bar{F}$  to obtain optimized POS for F

- SOP solution (Blue):

- Combining 1's in K-Map of F

$$F(A,B,C,D) = A + \overline{B}D$$

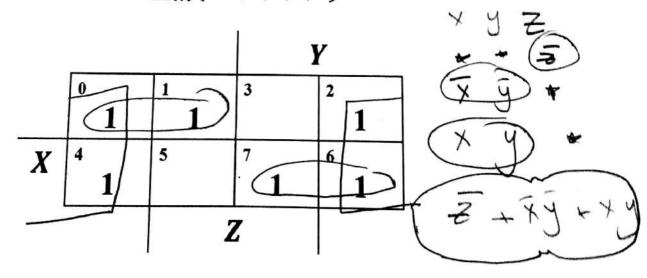

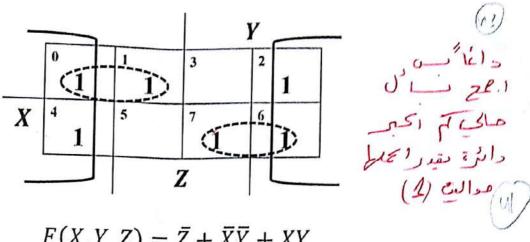

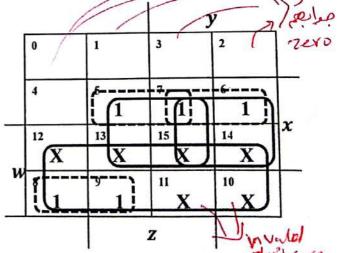

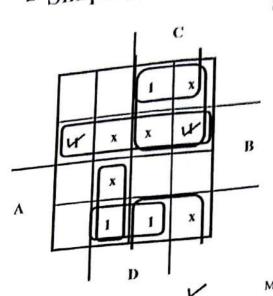

## Don't Cares in K-Maps

- Incompletely specified functions: Sometimes a function table or map contains entries for which it is known: dowl lare

- · the input values for the minterm will never occur, or

The output value for the minterm is not used

- In these cases, the output value is defined as a "don't care"