# Embedded Notes By: Asma Hakouz

# Getting Started with Embedded Systems

Chapter 1

Sections 1-6

Dr. Iyad Jafar

#### **Outline**

- What is an Embedded System?

- The Essence of Embedded Systems

- Embedded systems examples

- Some Computer Essentials

- Microprocessors vs. Microcontrollers

- The PIC Microcontroller

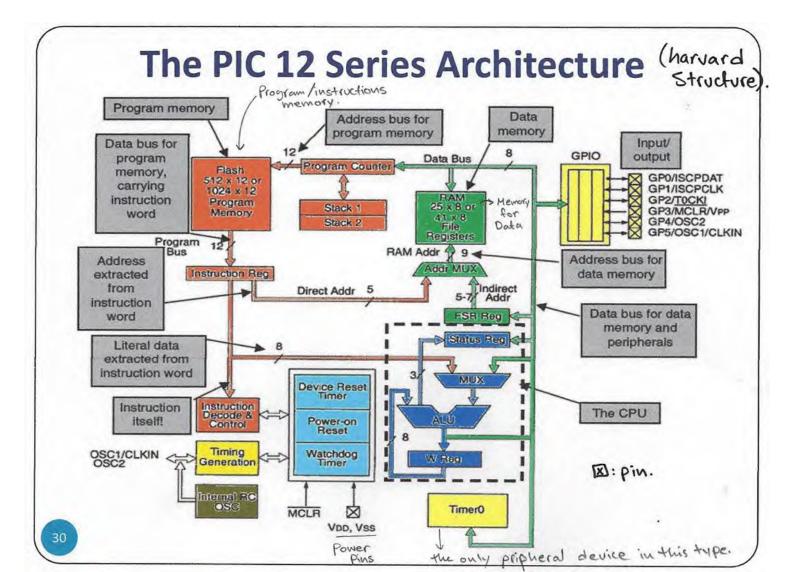

- The PIC 12 Series as an Example

#### What is an Embedded System?

- An embedded system is a computer system that is

- designed to perform <u>one or a few</u> dedicated functions often with <u>real-time computing</u> constraints

- embedded as part of a complete device often including hardware and mechanical parts.

- By contrast, a general-purpose computer, such as a personal computer, is designed to be flexible and to meet a wide range of end-user needs.

3

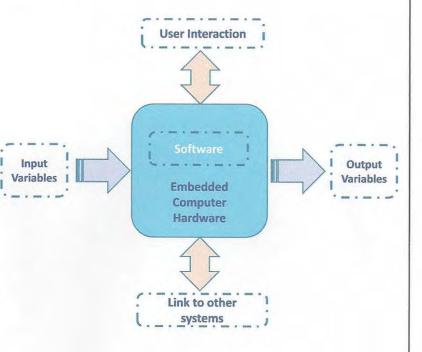

# Input Variables Link to other systems User Interaction Output Variables Link to other systems

#### The Essence of Embedded Systems

- Characteristics

- Microcontroller or DSP based

- Software driven

- Reliable

- Real-time control system

- Autonomous / human interactive / network interactive

- Operate on diverse input variables and in diverse environments

5

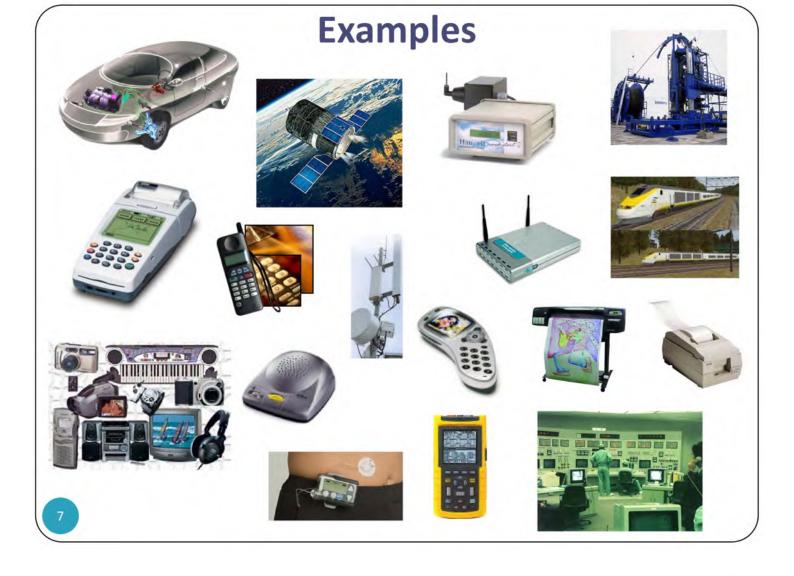

#### **Examples**

- Automotive

- Avionics/Aerospace/Defence

- Industrial Automation

- Telecommunications

- Consumer Electronics & Intelligent Homes & Retail (Thin Clients/POS)

- Scientific & Medical Equipment

- Computer peripherals

#### **Examples**

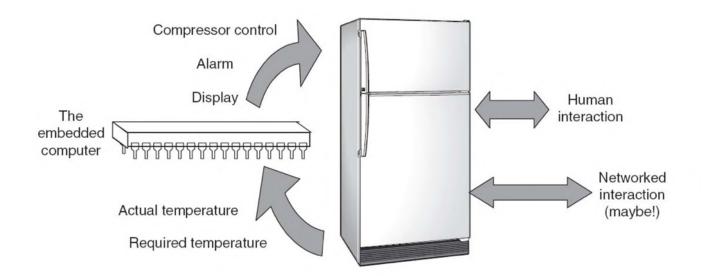

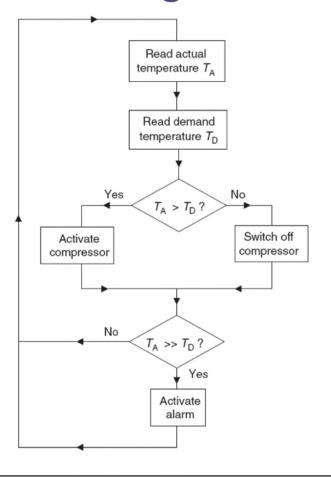

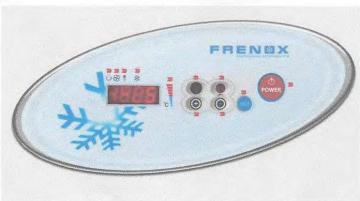

The refrigerator is required to maintain low temperature by reading the current value and controlling the compressor accordingly

#### **Examples**

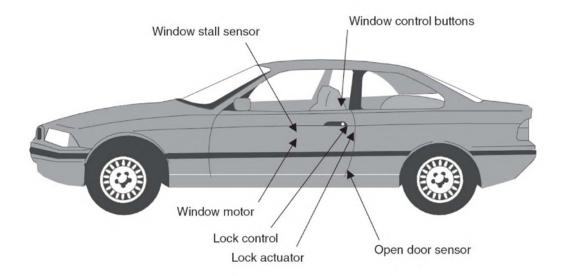

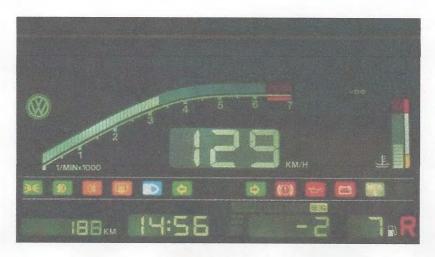

Different sensors in the car door produce signals that are of great importance when integrated with the rest of the car functionality

9

#### **Examples**

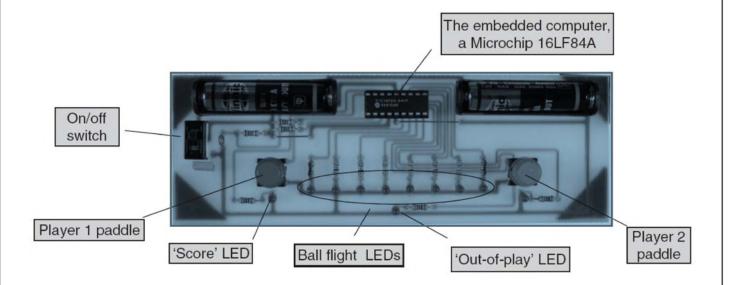

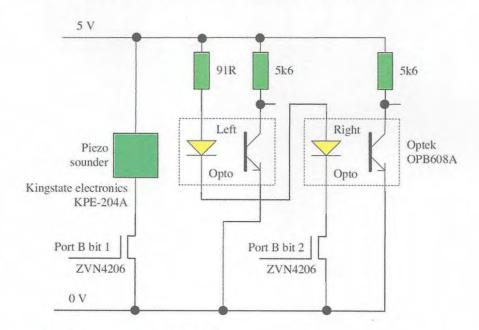

The Electronic 'ping-pong'

#### **Examples**

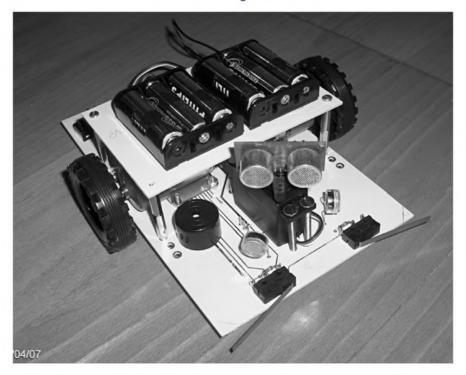

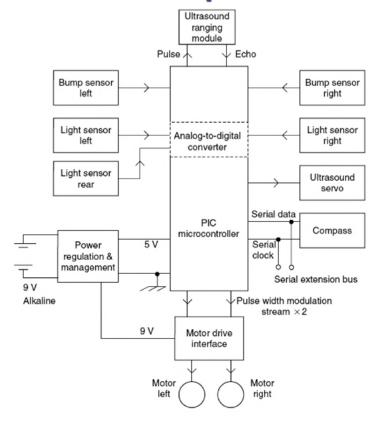

- The Derbot Autonomous Guided Vehicle

- More sensors and powerful microcontroller

#### **Examples**

The Derbot Autonomous Guided Vehicle

12

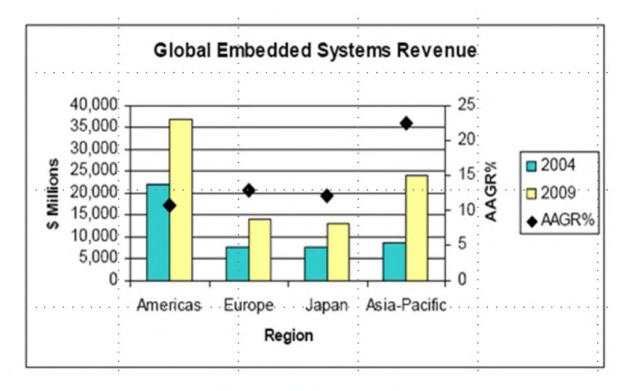

#### **Embedded Systems Market**

Source: BCC research <a href="http://www.bccresearch.com">http://www.bccresearch.com</a>

#### 13

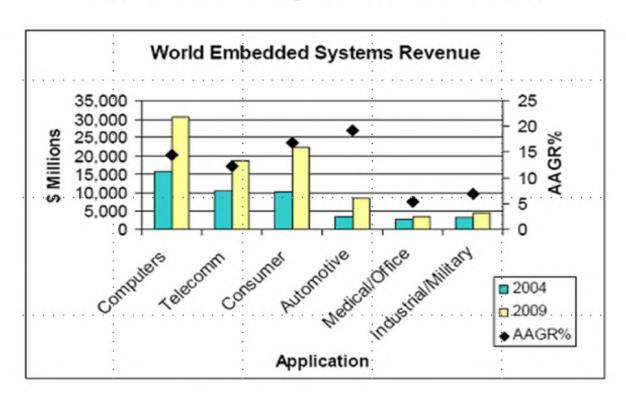

#### **Embedded Systems Market**

Source: BCC research <a href="http://www.bccresearch.com">http://www.bccresearch.com</a>

#### **Some Computer Essentials**

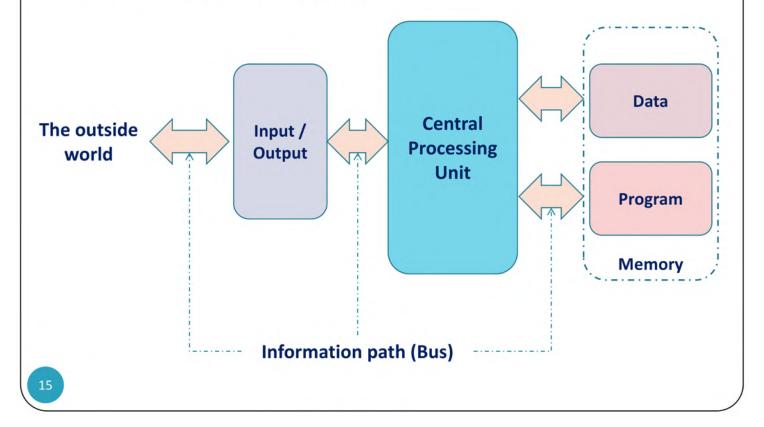

Elements of a Computer

#### **Some Computer Essentials**

#### **Memory Organization**

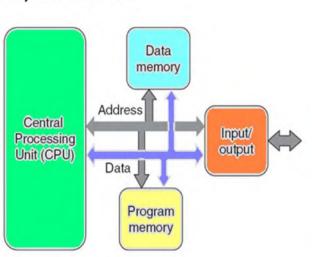

#### The Von Neumann Architecture

- One address bus and one data bus

- I/O may be also connected to these busses

- Simple and logical architecture, however

- Same memory width for instruction and data ?!

- Shared busses ?!

#### **Some Computer Essentials**

#### **Memory Organization**

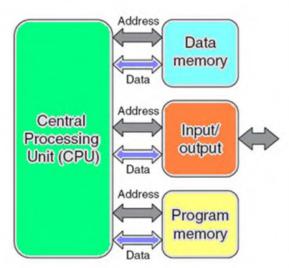

#### The Harvard Architecture

- Separate address and data bus for program memory and data memory

- More flexibility;

- Different memory width

- Simultaneous access of data and program memories

- Complex ?!

17

### Some Computer Essentials Instruction Sets

- Every CPU has a set of instructions that it can recognize and execute

- There are different approaches in designing instructions for the CPU in attempt to speed up program execution

- CISC (Complex Instruction Set Computers)

- Many instructions and addressing modes

- Instructions have different levels of complexity (different size and execution time)

- Relatively slow

- Shorter programs

- RISC (Reduced Instruction Set Computers)

- Few instructions and addressing modes

- Simple instructions of fixed size

- Relatively fast

- Longer programs

#### **Some Computer Essentials**

#### Memory Types

- Volatile

- Holds its contents as long as power is ON

- Used as temporary <u>storage to hold data</u>

- Easy to write

- RAM

#### Non-volatile

- Retains its values on power out

- More difficult to write in terms of time and power

- In embedded systems, it is <u>usually used to store programs</u>

- ROM

19

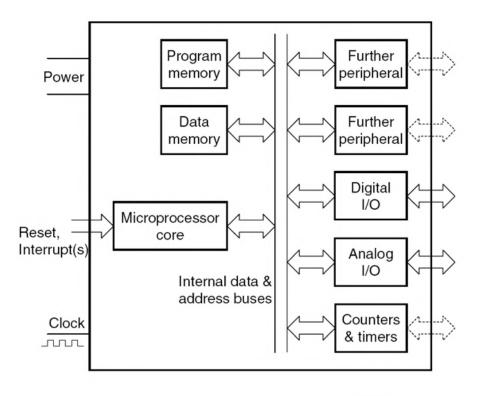

#### **Microprocessors and Microcontrollers**

- First microprocessors in the 1970s

- The computer CPU on a single chip

- Initially, memory and I/O interfacing outside the CPU

- As technology evolved, the microprocessor became more self-contained, powerful, and faster

- A special category of microprocessors emerged

- Microcontrollers

- Intended for control purposes

- No high computational power, huge memories, or high speed is required

- Has excellent I/O capabilities

- Small, low cost, and self contained

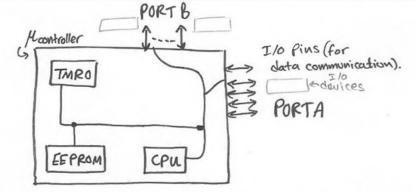

#### **Microprocessors and Microcontrollers**

A generic microcontroller

#### **Microprocessors and Microcontrollers**

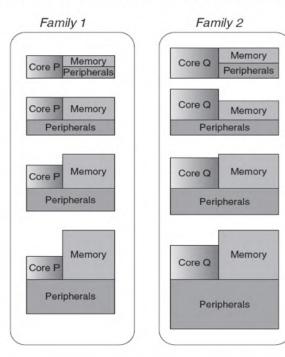

- Microcontroller Families

- Different families with <u>each family built around the same core</u>

- Family members differ in memory size and peripheral capabilities

21

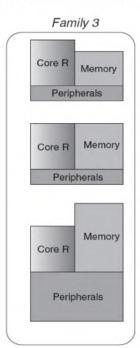

#### **Microprocessors and Microcontrollers**

- Microcontroller Packaging

- Plastic packaging

- Pins for I/O, clock, communication, and Power.

- The number of pins usually determines the size of the chip

23

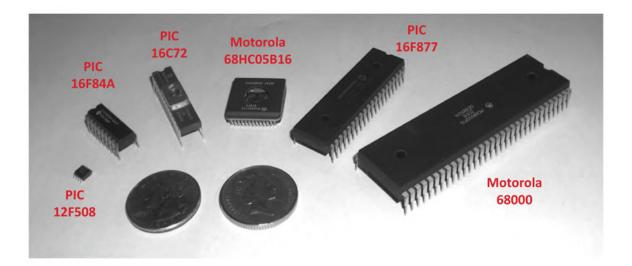

#### Microchip and the PIC Microcontrollers

- Peripheral Interface Controller (PIC) was originally a design by General Instruments intended for simple control applications

- In the late 1970s, GI introduced PIC® 1650 and 1655

- Standalone design

- RISC with 30 instructions

- Single working register (accumulator)

- Many attractive features

- PIC was sold to Microchip

#### Microchip and the PIC Microcontrollers

25

#### Microchip and the PIC Microcontrollers

#### Microchip and the PIC Microcontrollers

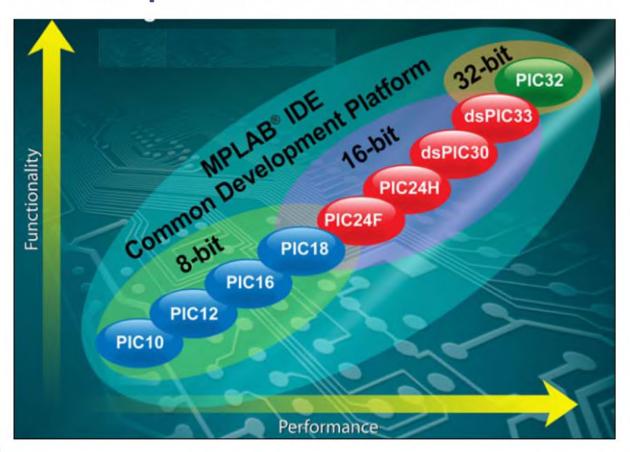

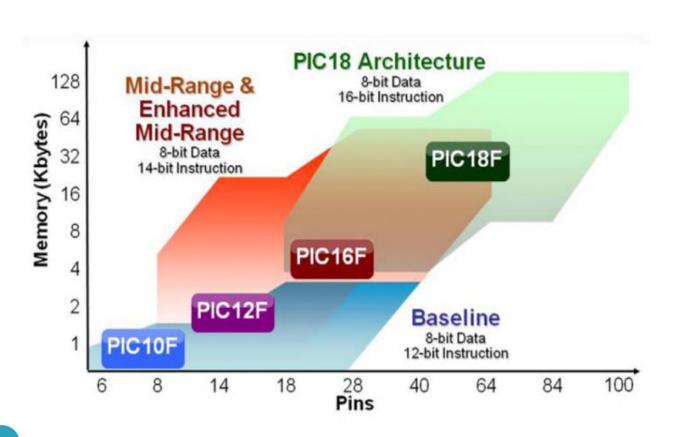

#### PIC Families

| PIC Family  | Stack Size<br>(words) | Instruction<br>Word Size | No. of<br>Instructions | Interrupt<br>Vectors |

|-------------|-----------------------|--------------------------|------------------------|----------------------|

| 12CX/12FX   | 2                     | 12- or 14-bit            | 33                     | None                 |

| 16C5X/16F5X | 2                     | 12-bit                   | 33                     | None                 |

| 16CX/16FX   | 8                     | 14-bit                   | 35                     | 1                    |

| 17CX        | 16                    | 16-bit                   | 58                     | 4                    |

| 18CX/18FX   | 32                    | 16-bit                   | 75                     | 2                    |

Example: the 16C84 was the first of its kind built using CMOS technology. It was later reissued as 16F84A incorporating flash memory and other technological features

#### Microchip and the PIC Microcontrollers

- PIC Characteristics

- Low-cost

- Self-contained

- 8-bit

- Harvard architecture

- RISC

- Pipelined

- Single accumulator (the working or W register)

- Fixed reset and interrupt vectors

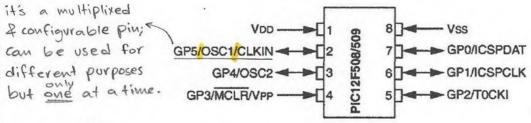

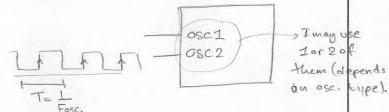

#### The PIC 12 Series

- PIC 12F508/509

- F: Flash memory

- The smallest and simplest PIC

Key

V<sub>DD</sub>:

Power supply

V<sub>SS</sub>:

Ground

V<sub>PP</sub>:

Programming voltage input

MCLR:

Master clear

OSC1, OSC2:

Oscillator pins

CLKIN:

External clock input

GP0 to GP5:

General-Purpose input/output pins (bidirectional except GP3)

CSPDAT: CSPCLK:

In-Circuit Serial Programming™ data pin. In-Circuit Serial Programming™ clock pin.

#### **Summary**

- An embedded system has one or more computers embedded within it that perform control operations

- A microcontroller is at the heart of embedded systems. It is basically a microprocessor with extended I/O capabilities

- Microchip is one of the popular vendors for a large variety of microcontrollers with different features

# Introducing the PIC 16 Series and the 16F84A

Chapter 2

Sections 1-8

Dr. Iyad Jafar

#### **Outline**

- Overview of the PIC 16 Series

- An Architecture Overview of the 16F84A

- The 16F84A Memory Organization

- Memory Addressing

- Some Issues of Timing

- Power-up and Reset

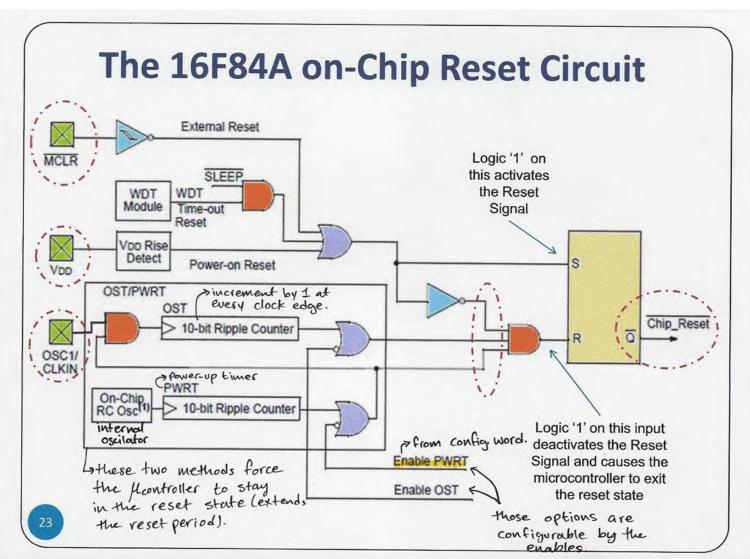

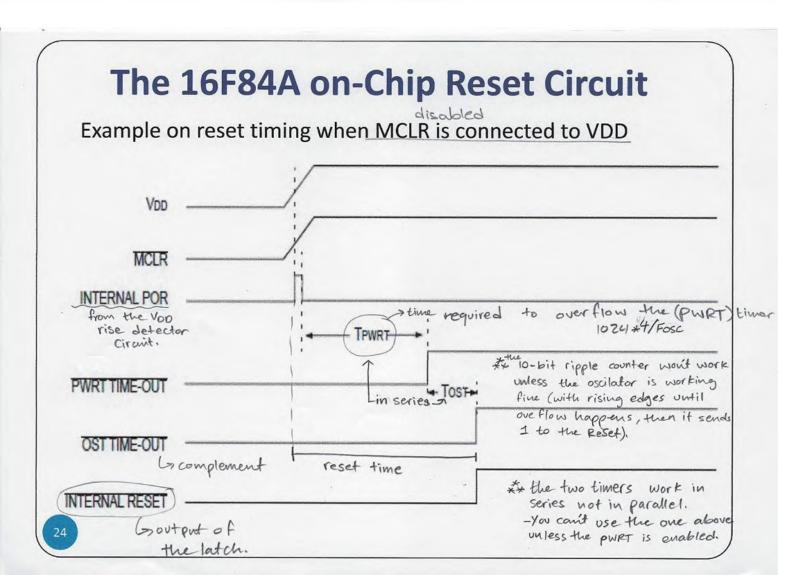

- The 16F84A On-chip Reset Circuit

## Overview of the PIC 16 Series

- The PIC 16 series is classified as a mid range microcontroller

- The series has different members all built around the same core and instruction set, but with different memory, I/O features, and package size

3

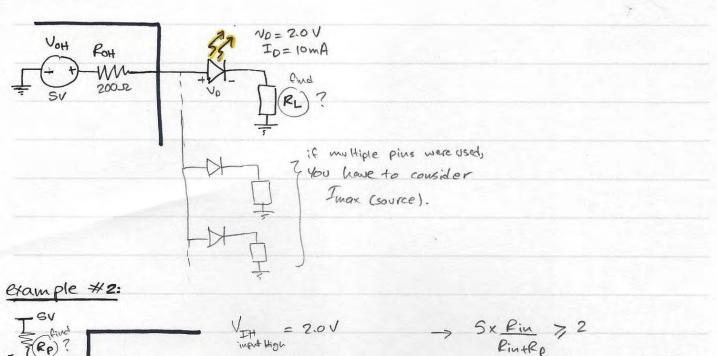

| Device<br>number | No. of pins* | . Clock speed | Memory<br>(K = Kbytes, i.e. 1024 bytes)                 | Peripherals/special features                                                                                                                   |

|------------------|--------------|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 16F84A           | 18           | DC to 20 MHz  | 1K program memory,<br>68 bytes RAM,<br>64 bytes EEPROM  | 1 8-bit timer<br>1 5-bit parallel port<br>1 8-bit parallel port                                                                                |

| 16LF84A          | As above     | As above      | As above                                                | As above, with extended supply voltage range                                                                                                   |

| 16F84A-04        | As above     | DC to 4 MHz   | As above                                                | As above                                                                                                                                       |

| 16F873A          | 28           | DC to 20 MHz  | 4K program memory<br>192 bytes RAM,<br>128 bytes EEPROM | 3 parallel ports, 3 counter/timers, 2 capture/compare/PWM modules, 2 serial communication modules, 5 10-bit ADC channels, 2 analog comparators |

| 16F874A          | 40           | DC to 20 MHz  | 4K program memory<br>192 bytes RAM,<br>128 bytes EEPROM | 5 parallel ports, 3 counter/timers, 2 capture/compare/PWM modules, 2 serial communication modules, 8 10-bit ADC channels, 2 analog comparators |

| 16F876A          | 28           | DC to 20 MHz  | 8K program memory<br>368 bytes RAM,<br>256 bytes EEPROM | 3 parallel ports, 3 counter/timers, 2 capture/compare/PWM modules, 2 serial communication modules, 5 10-bit ADC channels, 2 analog comparators |

| 16F877A          | 40           | DC to 20 MHz  | 8K program memory<br>368 bytes RAM,<br>256 bytes EEPROM | 5 parallel ports, 3 counter/timers, 2 capture/compare/PWM modules, 2 serial communication modules, 8 10-bit ADC channels, 2 analog comparators |

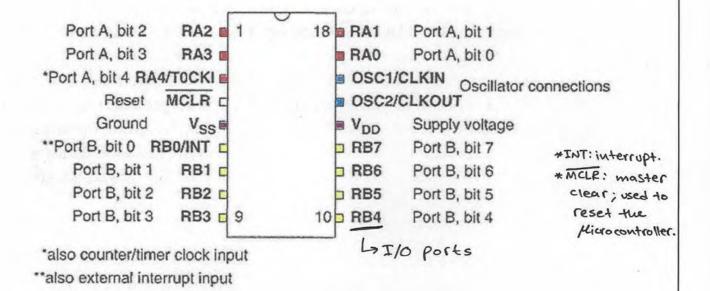

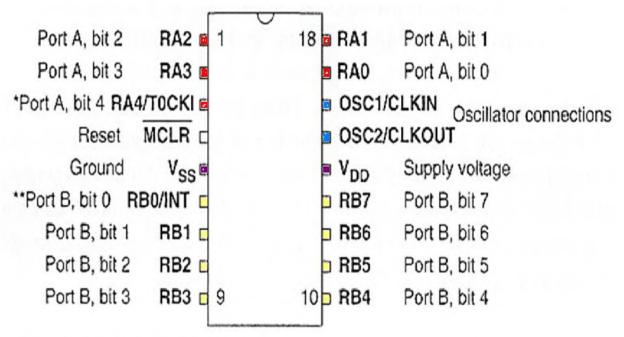

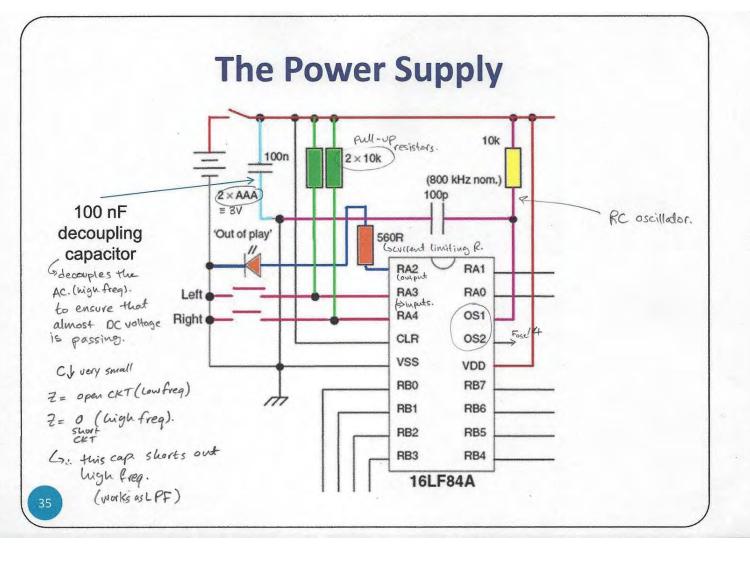

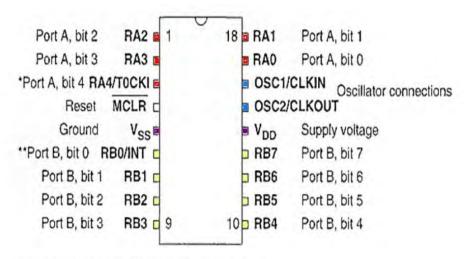

The general Pin-out for PICIEF84A:

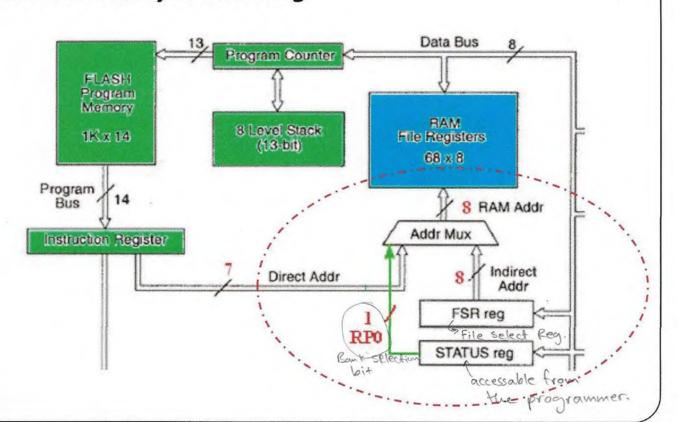

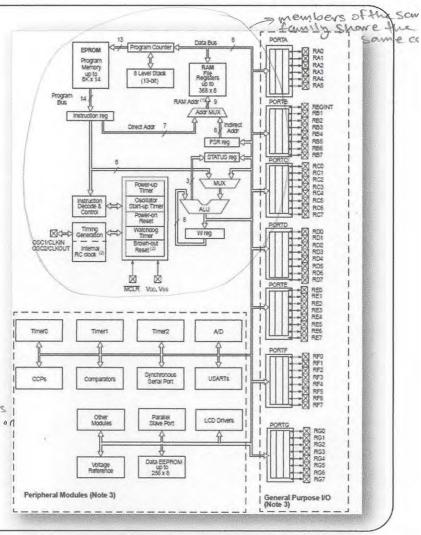

# An Architecture Overview of the 16F84A

• 18 Pins / DC to 20MHz / 1K program Memory/ 68 Bytes of RAM / 64

Bytes of EEPROM / 1 8-bit Timer / 1 5-bit Parallel Port / 1 8-bit Parallel

Port | Electrically Erasa ble Programmable ROM:

Port | Electrically Erasa ble Programmable ROM:

Used to store data permenantly (even when we turn off the system)

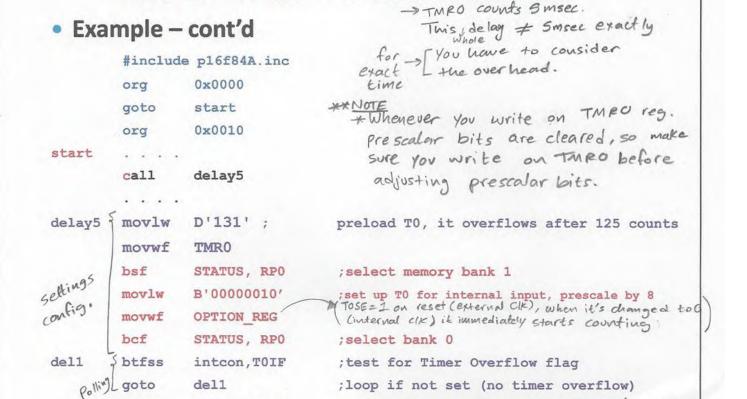

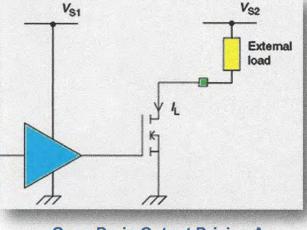

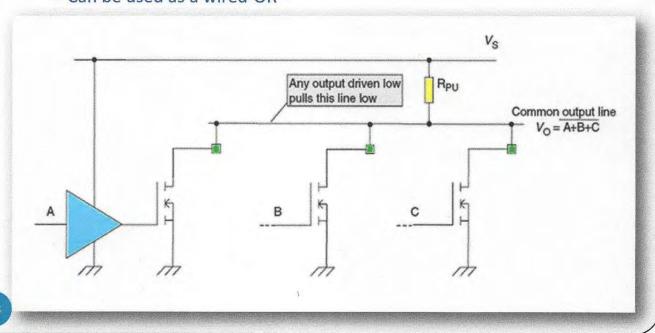

An Architecture Overview of the 16F84A for PICIEF844 we only need 10-bits to address all mem. locations (IK) but this (13) is for (PICF16) Family in general (addresses &K locations) Program Counter **EEPROM Data Memory** SRAM Program Memory non-volatile EEPROM memory. 8 Level Stack **EEDATA** Data Memory 64 x 8 1K x 14 (13-bit) Program 8 RAM Addr EEADR Addr Mux Instruction Register SRAM Indirect **TMRO** Direct Addr Counter/Timer Addr 'Timer0' FSR reg RP0 RA4/TOCK STATUS reg imer O Clock input. Port A MUX I/O Ports 8 ALL Control RA3:RA0 Timing **RB7:RB1** W rea Generation Port B RB0/INT MCLR OSC2/CLKOUT VDD, VSS OSC1/CLKIN

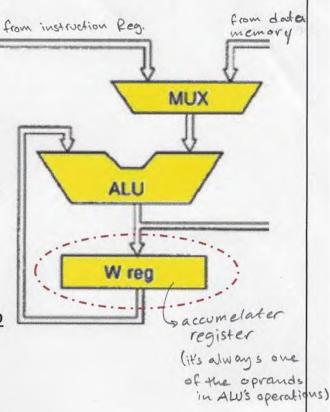

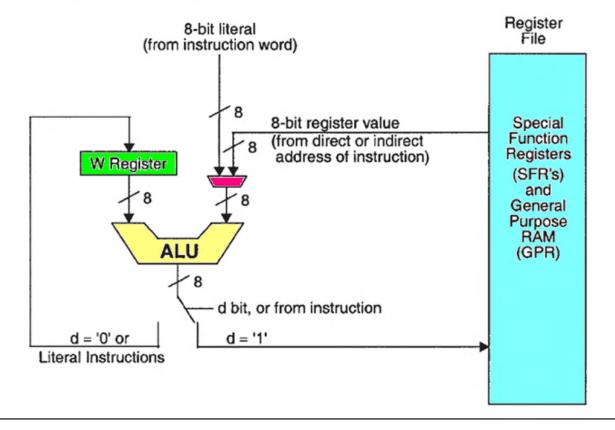

# The PIC 16F84A ALU and Working Register

#### Arithmetic & Logic Unit

- 8-bit ALU

- Supports 35 simple instructions

- Input operands are

- The working register

- Content of some file register or a literal

- The result is stored in Working register or in a File register

#### The Working Register

- Inside the CPU

- For many instructions, it can be chosen to hold the result of the last instruction executed by the CPU

7

#### The PIC 16F84A Memory Organization

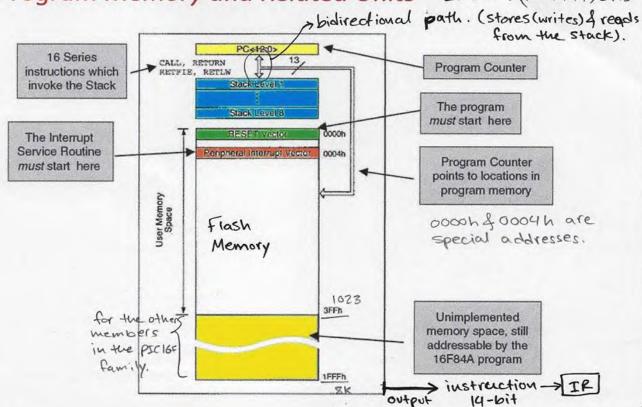

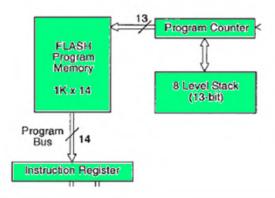

• Program Memory and Related Units 1 × 14 = (1024 × 14) bits

|                                       |                                              |                  | the address of the naddresses not data |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------|----------------------------------------------|------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       |                                              | tile) memory.    |                                        | stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| * My program                          | must stav                                    | t ad 0000 H      | ; since this is the c                  | iddress the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| the PIC will                          | first consult                                | upon power-      | op.                                    | STEENSON PRODUCTION OF THE PRO |

| address or in                         | rogram; at<br>counter<br>studion<br>pointer. | least 10-bits wi | dth. (for PICIEF84A)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| * TR (Tustruction instruction 14-bits | ion Register                                 | : stores the iu  | astruction being e                     | recuted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Sfrom the program                     | memory.                                      |                  |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                       |                                              |                  |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

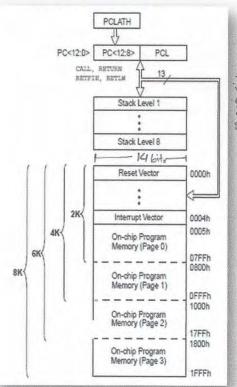

#### The PIC 16F84A Memory Organization

#### Program Memory

- 1K x 14 Bits

- Address range 0000H 03FFH

- Flash (nonvolatile)

- 10000 erase/write cycles

- Location 0000H is reserved for the reset vector

- Location 0004H is reserved for the Interrupt Vector

#### Program Counter

Holds the address of the instruction to be executed (next instruction)

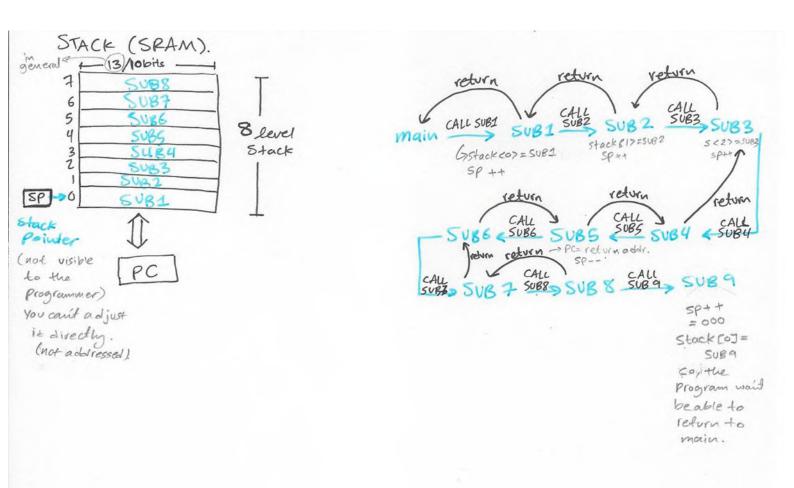

#### Stack

- 8 levels (each is 13 bits)

- SRAM (volatile)

- Used to store/load the return address with instruction like CALL, RETURN,RETFIE, and RETLW (interrupts and subroutines)

#### Instruction Register

· Holds the instruction being executed

#### The PIC 16F84A Memory Organization

#### The Configuration Word (used to store some data to configure the Microcontroller.

- A special part of the program memory (beyond 8k)

Ox 2007

- Allows the user to configure different features of the microcontroller at the time of program download and is not accessible within the program or while it is running

| R/P-u   | R/P-u | R/P-u                      | R/P-u                                                       | R/P-u             | R/P-u     | R/P-u     | R/P-u | R/P-u | R/P-u       | R/P-u                        | R/P-u                 | R/P-u    | R/P-u      |

|---------|-------|----------------------------|-------------------------------------------------------------|-------------------|-----------|-----------|-------|-------|-------------|------------------------------|-----------------------|----------|------------|

| CP      | CP    | CP                         | CP                                                          | CP                | CP        | CP        | CP    | CP    | CP          | PWRTE                        | WDTE                  | F0SC1    | F0SC0      |

| oit13   | -     |                            |                                                             |                   |           | т         |       |       |             |                              |                       |          | bitO       |

| it 13-4 |       | 1 = Co                     | ode Prote<br>de prote<br>program                            | ction dis         | abled     | e protec  | ted 🥕 | to p  | gevent      | anyo                         | ne from               | un acce  | esing you  |

| oit 3   |       | 1 = Po                     | E: Powe<br>wer-up T<br>wer-up T                             | imer is           | disabled  |           |       | 4     | e R/F       | Su:                          | r the (               | -) is th | ne default |

| oit 2   |       | 1 = WE                     | Watchd<br>T enabl<br>T disab                                | ed                | r Enabl   | e bit     |       | -     | P: 40       | n be r                       | write                 | e oni    | + only     |

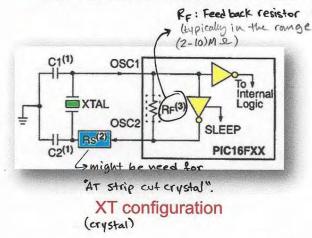

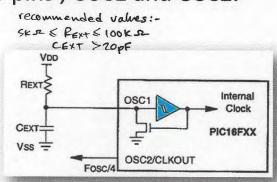

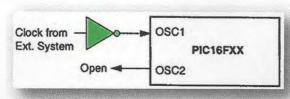

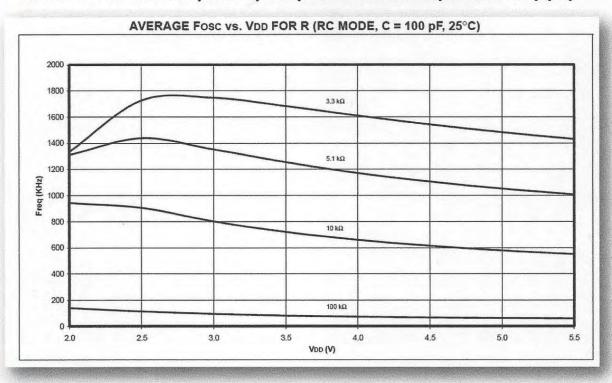

| oit 1-0 |       | 11 = R<br>10 = H<br>01 = X | I:FOSC(<br>C oscilla<br>S oscilla<br>T oscilla<br>P oscilla | tor<br>tor<br>tor | ator Sele | ection bi | ts    | -     | program: it | rammin<br>ts value<br>ser-de | g.<br>eat s<br>efined | start-   | up is      |

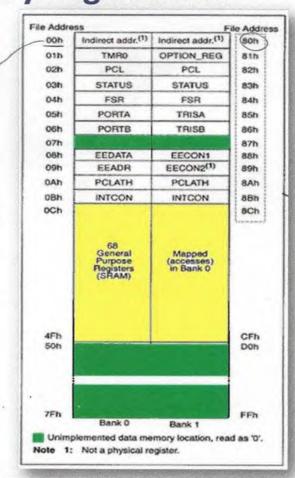

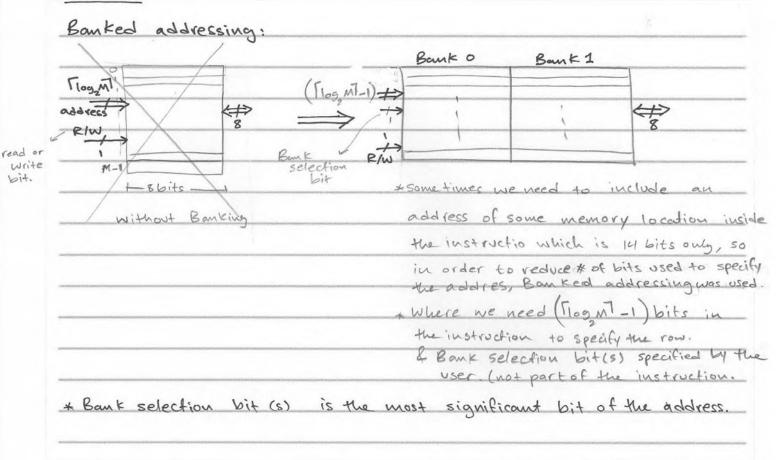

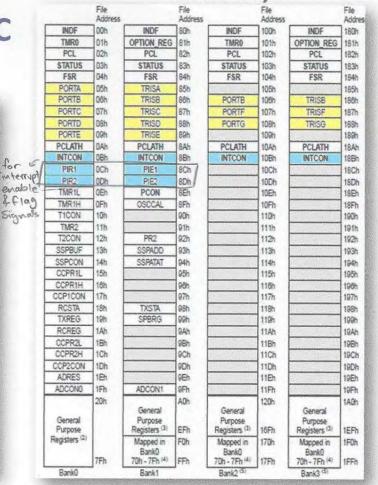

#### The PIC 16F84A Memory Organization

#### Data Memory and Special Function Registers (SFRs)

- SRAM (volatile)

- eank selection

- Banked addressing

- 80h > 1000 0000 Bank1

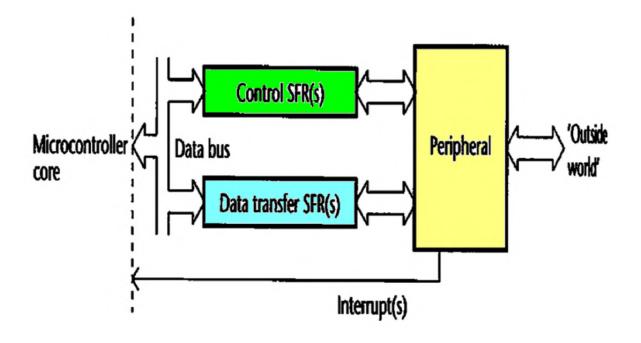

#### Special Function Registers SFRs

- Locations 01H-0BH in bank 0 and 81H-8BH in bank 1

- Used to communicate with I/O and control the microcontroller operation

- Some of them hold I/O data

#### General Purpose Registers

- Addresses OCH 4FH (68 Bytes)

- Used for storing general data

#### The PIC 16F84A Memory Organization Special Function Registers (SFRs) Address Bank 0 Address Bank 1 INDF: Data memory contents by indirect addressing 00h INDF frequently TMRO: Timer counter TMRO 01h OPTION RE 81h used PCL: Low order 8 bits of program counter Reg. 02h PCL+ 82h STATUS: Flag of calculation result accessing 83h 03h both ozh FSR: Indirect data memory address pointer 282 his 04h 84h PORTA: PORTA DATA I/O the same 05h 85h PORTB: PORTB DATA I/O Since both 06h 86h are PCL EEDATA: Dtata for EEPROM. 07h Unimplemented 87h (when you EEADR: Address for EEPROM access 824 88h 160 PCLATH: Write buffer for upper 5 bits of the program counter you redirected 19th EEADH EECON2 89h INTCON: Interruption control to 92h). OAh 8Ah OPTIN REG: Mode set thus, we INTEGEN. 8Bh 0Bh don't need a bank TRISA: Mode set for PORTA selection Och - 4Fh TRISB: Mode set for PORTB GPR 8Ch - CFh bit here. EECON1: Control Register for EEPROM EECON2: Write protection Register for EEPROM

#### The PIC 16F84A Memory Organization

Special Function Registers (SFRs) interacting with peripherals

File Registers

GPR

General Purpose

Special Function

Reg.

M-C related I/O & prepherals

(INTCON)

(STATUS)

data Control

#### The PIC 16F84A Memory Organization

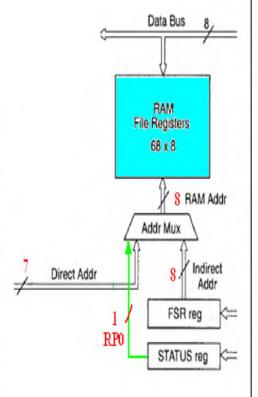

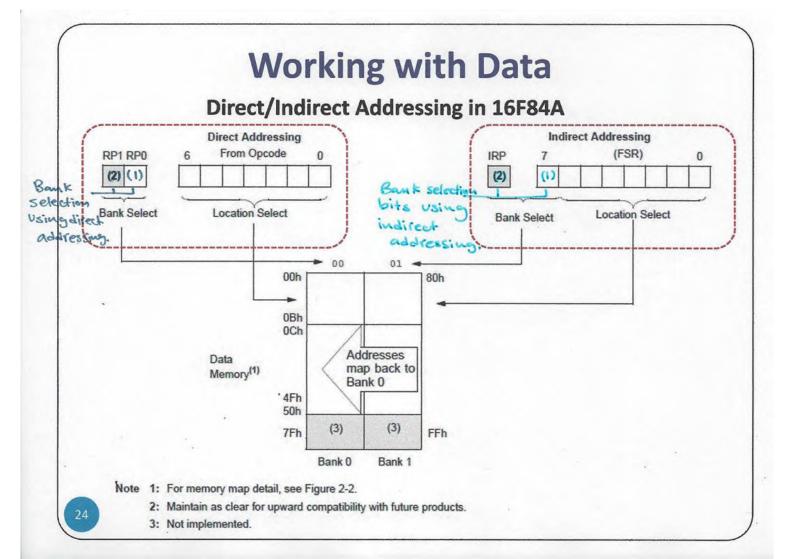

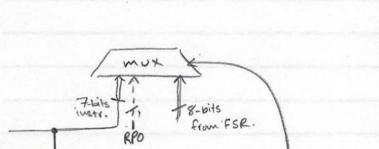

- Data Memory Addressing

- For PIC 16F84A, the address of any memory location (File Register is 8 bits

- One bit is used to select the bank

- Seven bits to select a location in the bank

- Bank selection is done through using <u>bits 5 and 6 of the STATUS</u> registers (RPO and RP1)

- For the 16F84A, only RPO is needed since we have two banks

- In general, two forms to address the RAM (File Registers)

- Direct addressing the 7-bit address is part of the instruction + bank selection

bit (s) from

Status Reg

- Indirect addressing

- the 7-bit address is loaded in lower 7 bits of the File Select Register (FSR, 04H)

- Bank selection is done using the <u>most significant bit of FSR</u> and the IRP bit in the STATUS register

G if more than 2 banks are used.

14

#### The PIC 16F84A Memory Organization

Data Memory Addressing

#### The PIC 16F84A Memory Organizat

- Data Related

- EEPROM Data Memory

- 64 bytes Non-volatile

- 10 000 000 erase/write cycles

- Used to store data that is likely to be needed for long term

- Oaddress Operation is controlled through EEDATA (08H), EEADR (09H), EECON1 3 Pata (88H), and EECON2 (89H) SFRs 3 A/W bi

**EEPROM Data Memory**

17 EEADR

unicote

EEDATA non-voladile

- To read a location

- store the address in EEADR and set the RD bit in EECON1

- data is copied to EEDATA register

- To write to a location

- data and address are placed in EEDATA and EEADR, respectively

- enable writing by setting the WREN bit in EECON1 SFR

- store 55H then AAH in EECON2

- commit writing by enabling the WR bit

- Once the write is done, the EEIF flag is set in EECON1.

long procedure for protection to prevent Writing by mistake.

#### The PIC 16F84A Memory Organization

The EECON1 Register (88H)

| U-0 | U-0 | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-----|-----|-----|-------|-------|-------|-------|-------|

| -   |     |     | EEIF  | WRERR | WREN  | WR    | RD    |

> Programmer.

bit 7-5 Unimplemented: Read as '0'

bit 4 EEIF: EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation is not complete or has not been started

bit 3 WRERR: EEPROM Error Flag bit

1 = A write operation is prematurely terminated

(any MCLR Reset or any WDT Reset during normal operation)

0 = The write operation completed

bit 2 WREN: EEPROM Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Write Control bit

1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

1 = Initiates an EEPROM read RD is cleared in hardware. The RD bit can only be set (not

cleared) in software.

0 = Does not initiate an EEPROM read

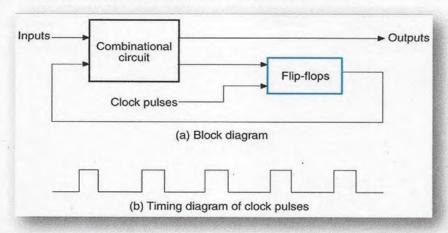

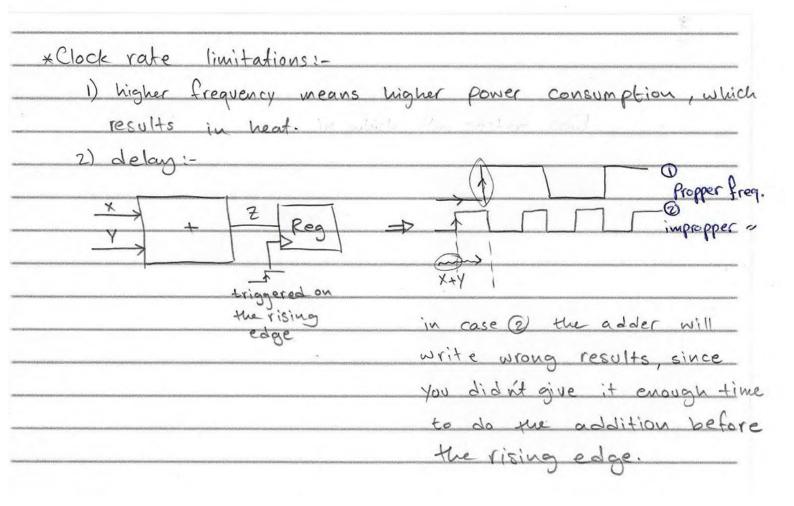

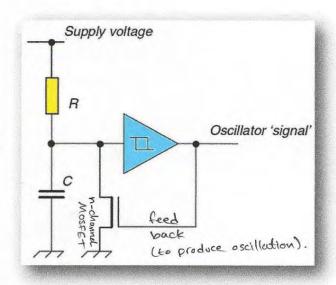

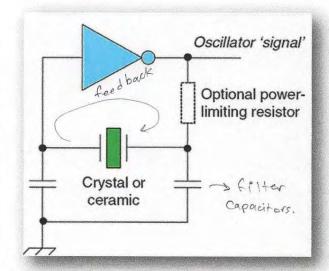

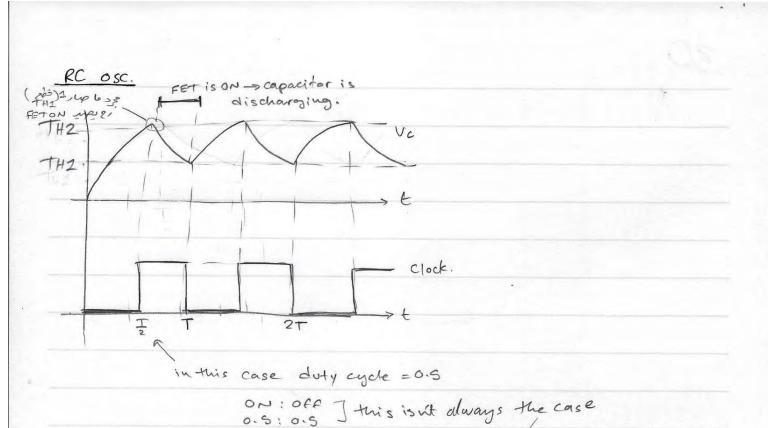

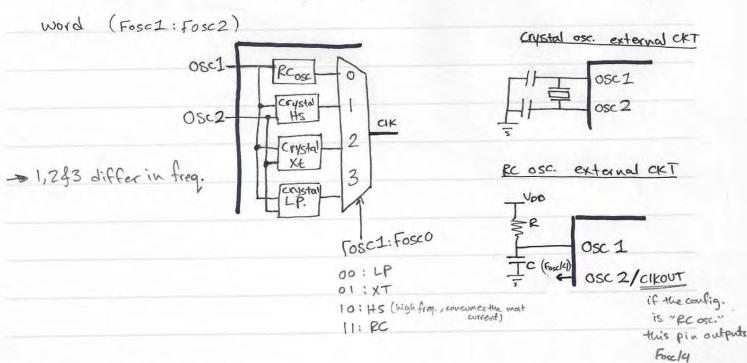

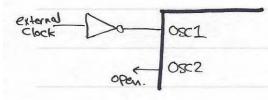

#### Some Issues of Timing

#### The Clock

- The microcontroller is made up of combinational and sequential logic.

Thus, it requires a clock!

- Clock a continuously running fixed frequency logic square wave

- <u>Timers, counters, serial communication functions are also dependent</u> on the clock

- Operating frequency has direct impact on power consumption

- Every microcontroller has a range for its clock → w hy? (next slide).

10

#### **Some Issues of Timing**

#### Instruction Cycle

- The main clock is divided by a fixed value (4 in the 16 series) into a lower-frequency signal

- The cycle time of this signal is called the instruction cycle

- The primary unit of time in the action of processor

| Clock frequency | Instruction cycle |           |  |  |  |

|-----------------|-------------------|-----------|--|--|--|

|                 | Frequency         | Period    |  |  |  |

| 20 MHz          | 5 MHz             | 200 ns    |  |  |  |

| 4 MHz           | 1 MHz             | 1 μs      |  |  |  |

| 1 MHz           | 250 kHz           | 4 μs      |  |  |  |

| 32.768 kHz      | 8.192 kHz         | 122.07 μs |  |  |  |

| if Fosc = 20MHz : freq. of the oscilator                                 |                                |

|--------------------------------------------------------------------------|--------------------------------|

| Tose = 1 = 0.5 pt sec.                                                   |                                |

| but in data sheet instruction's execution rate                           | is 20 M                        |

| Since in PIC Microcontrollers ou common do                               |                                |

| devices use a clock derivated from the such as CPU which needs UK rate = |                                |

|                                                                          | ethis is called instructions f |

| Tay = 4; instruction Cycle Fosc                                          |                                |

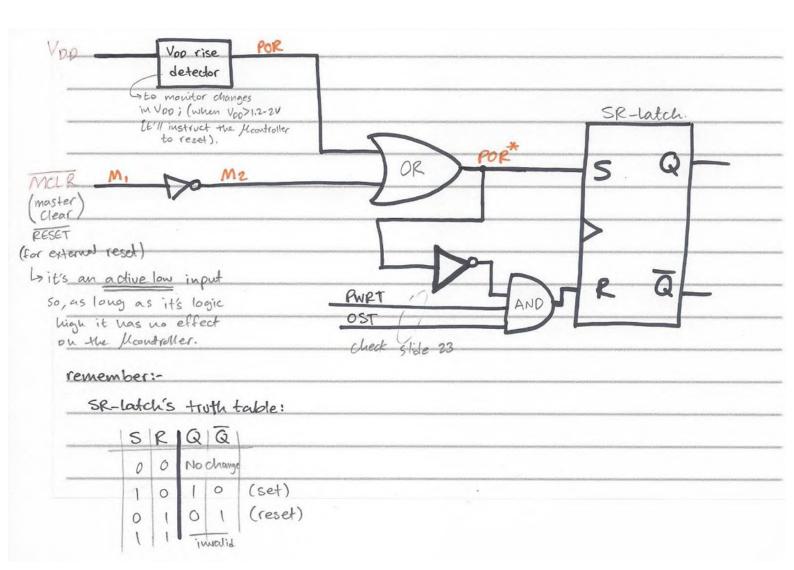

#### **Some Issues of Timing**

#### Pipelining

- Every instruction in the computer has to be fetched from memory and then executed. These steps are usually performed one after another

- The CPU can be designed to fetch the next instruction while executing the current instruction. This improves performance significantly!

- This is called Pipelining

- All PIC microcontrollers implement pipelining (RISC+Harvard make it easy)

by this we improved the

Time

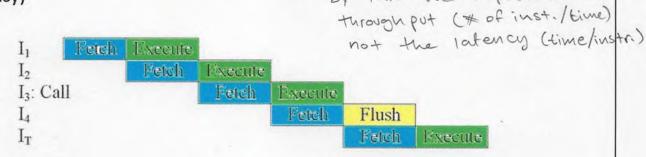

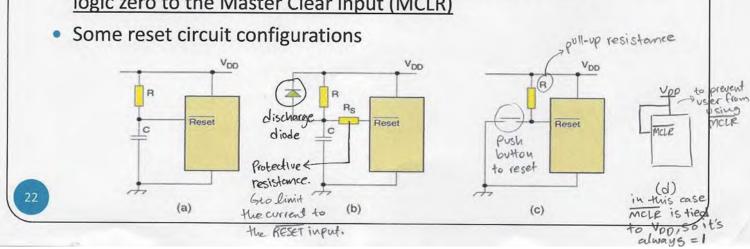

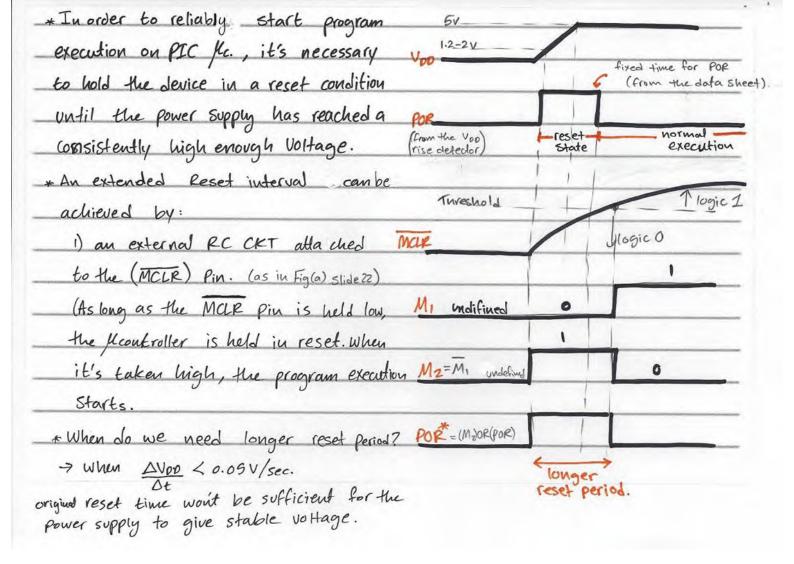

#### **Power-up and Reset**

- On power-up, the microcontroller must start to execute the program stored in the program memory from its beginning (address 0000H)

- A specialized circuit inside the microcontroller detects this and is responsible for putting the microcontroller in the reset state:

- the program counter is set to zero

- the SFRs are set such that the peripherals are in safe and disabled

- Another way to put the microcontroller in the reset state is to apply logic zero to the Master Clear input (MCLR)

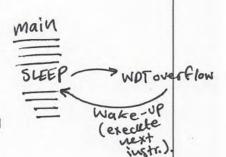

| wot module : interupt - | timer (Watch D  | og timer)                                                        |

|-------------------------|-----------------|------------------------------------------------------------------|

| -once it                | reaches its m   | aximum, it resets the Mcontroller (overflow)                     |

|                         | figurable by 4  | ne programmer (from the configuration                            |

| * Mountroller can enter | reset loased    | d on other factors than vop & MCLE                               |

|                         |                 |                                                                  |

| - V op & MCLR; ext      | ernal reset src | Z absence of those will get the . ) Montroller out of the reset. |

| * Where can we adj      |                 |                                                                  |

|                         |                 | ystal oscilator is connected.                                    |

|                         |                 | is defined from Fosco & Fosc1                                    |

| bits in the             |                 |                                                                  |

| Fosco                   | Fosc1 OSTE      |                                                                  |

| 7                       | 0               |                                                                  |

| 0                       |                 | OSTE = F, F2                                                     |

|                         | 0               | AND                                                              |

#### **Summary**

- The PIC 16F84A series is a diverse and cost effective family of microcontrollers

- The PIC 16F84A is pipelined RISC processor with Harvard architecture

- The PIC 16F84A has three different memory types

- An important memory area is the Special Function Register area which act as link between the CPU and peripherals

- Reset operation must be understood for proper operation of the microcontroller

25

#### Starting to Program

Chapter 4

Sections 1-4, 10

Dr. Iyad Jafar

#### **Outline**

- Introduction

- Program Development Process

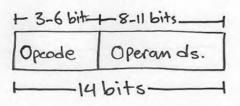

- The PIC 16F84A Instruction Set

- Examples

- The PIC 16F84A Instruction Encoding

- Assembler Details

- Sample Programs

2

#### Introduction

- Every computer can recognize and execute a group of instructions called the *Instruction Set*

- These instruction are represented in binary (machine code)

- A program is a sequence of instructions drawn from the instruction set and combined to perform specific operation

- To run the program:

- It is loaded in binary format in the system memory

- The computer steps through every instruction and execute it

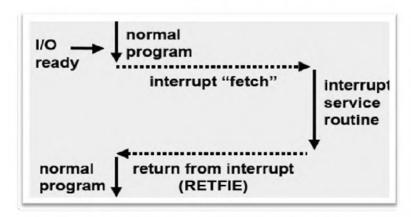

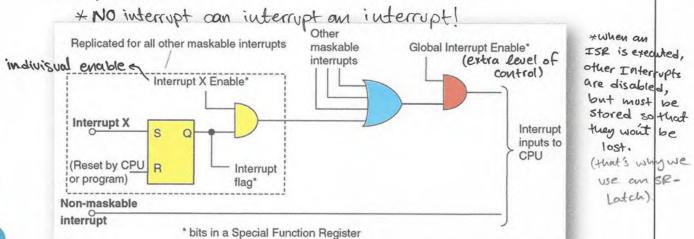

- Execution continues unless something stops it like the end of program or an interrupt

#### **How to Write Programs**

#### Machine code

- Use the binary equivalent of the instructions

- · Slow, tedious, and error-prone

00 0111 0001 0101

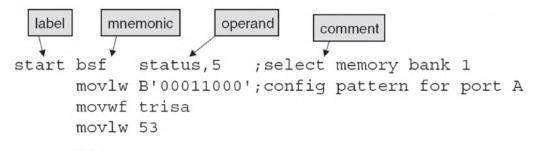

#### Assembly

- · Each instruction is given a mnemonic

- A program called Assembler converts to machine code

- · Rather slow and inefficient for large and complex programs

addw NUM, w

#### High-level language

- Use English-like commands to program

- A program called Compiler converts to machine code

- · Easy !! The program could be inefficient!

for (i=0; i<10; i++) sum += a[i];

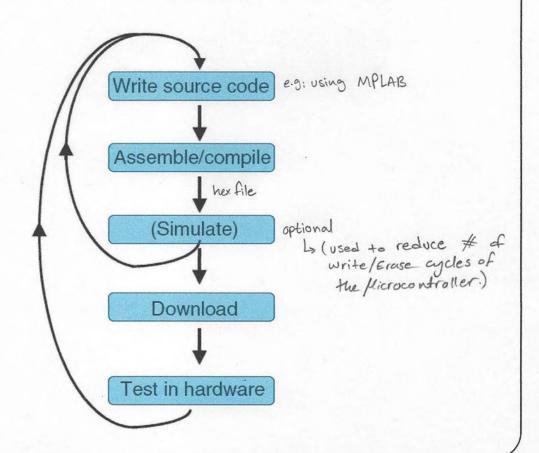

#### **Program Development Process**

compiler:- step high-level -> Assembly -> machine high-level -> Assembly -> machine

1

The PIC 16 Series ALU

#### The PIC 16 Series Instruction Set

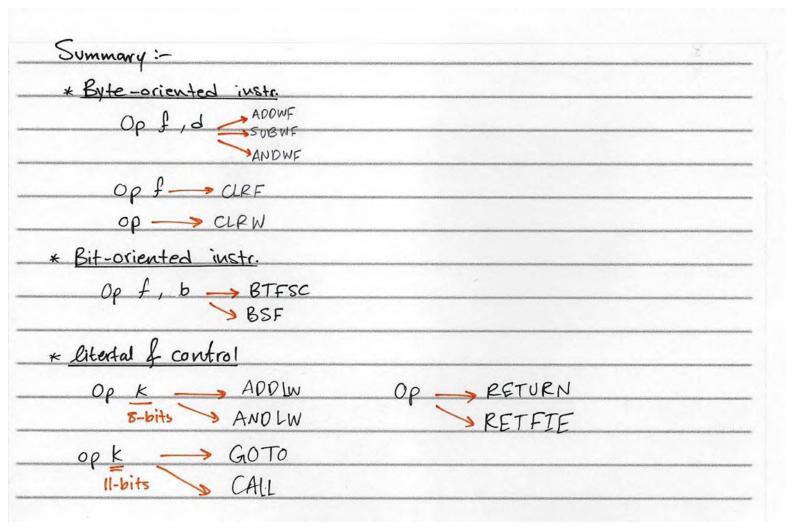

- 35 instructions !!! RISC (check Appendix 1 for the instruction set of PIC 16 series.)

- The binary code of the instruction itself is called the Opcode

- Most of these instruction operate/use on values called Operands (ranging from no operands to two)

- Three categories of instructions

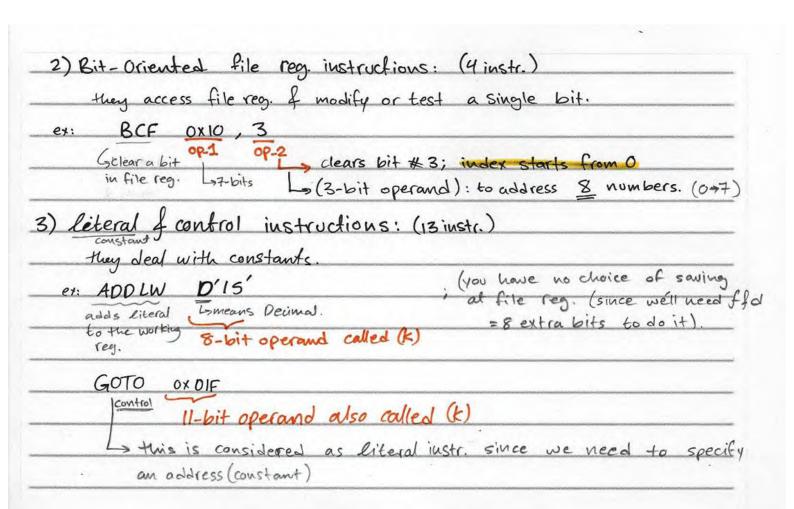

- Byte-oriented file register operations

- 2. Bit-oriented file register operations

- 3. Literal and control operations

- Type of operations

- 1. Arithmetic

- 2. Logic

- 3. Data movement

- 4. Control

- 5. Misc

6

TABLE A1.1 PIC 16 Series Instruction Set Summary

| Mnemonic,<br>operands |       |                              |        |     | 14 Bit | opcode |      | Status   | Notes |

|-----------------------|-------|------------------------------|--------|-----|--------|--------|------|----------|-------|

|                       |       | Description                  | Cycles | MSb |        |        | LSb  | affected |       |

| BYTE ORIE             | ENTED | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF                 | f,d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f,d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF                  | f     | Clear f                      | 1      | 00  | 0001   | Ifff   | ffff | Z        | 2     |

| CLRW                  |       | Clear W                      | 1      | 00  | 0001   | 0xxx   | xxxx | Z        |       |

| COMF                  | f,d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF                  | f,d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

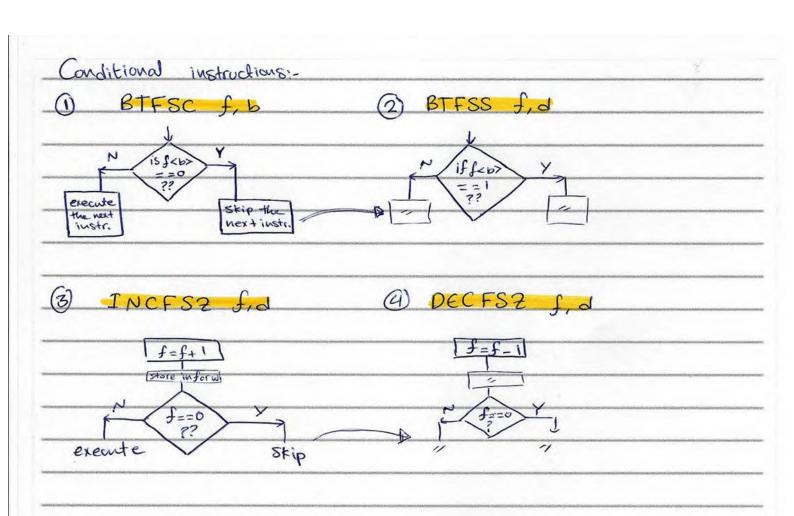

| DECFSZ                | f,d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF                  | f,d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| <b>INCFSZ</b>         | f,d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF                 | f,d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF                  | f,d   | Movef                        | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVW                  | f     | Move W to f                  | 1      | 00  | 0000   | Ifff   | ffff |          |       |

| NOP                   |       | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

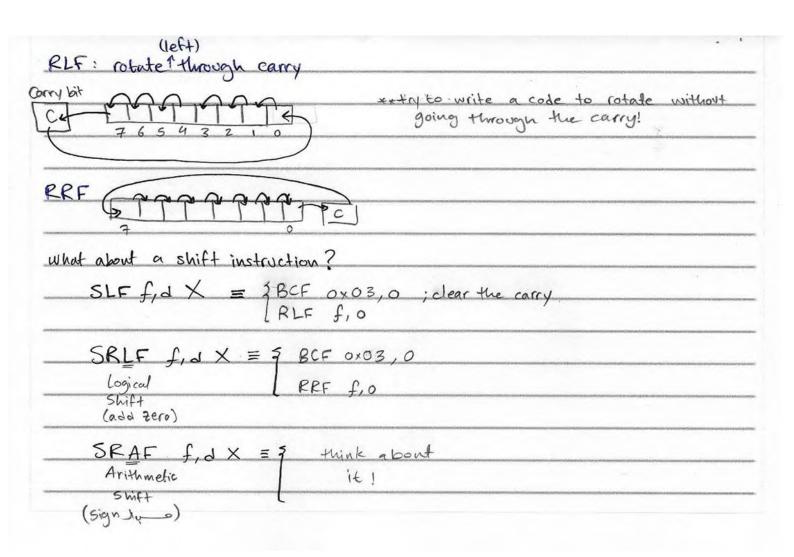

| RLF                   | f,d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | C        | 1,2   |

| RRF                   | f,d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | C        | 1,2   |

| Mnemonic,    |       |                             |        | 14 Bit opcode |      |      |             | Status   |       |

|--------------|-------|-----------------------------|--------|---------------|------|------|-------------|----------|-------|

| operands     |       | Description                 | Cycles | MSb           |      |      | LSb         | affected | Notes |

| SUBWF        | f,d   | Subtract W from f           | 1      | 00            | 0010 | dfff | ffff        | C,DC,Z   | 1,2   |

| <b>SWAPF</b> | f,d   | Swap nibbles in f           | 1      | 00            | 1110 | dfff | ffff        |          | 1,2   |

| XORWF        | f,d   | Exclusive OR W with f       | 1      | 00            | 0110 | dfff | <b>ffff</b> | Z        | 1,2   |

| BIT ORIEN    | TED F | FILE REGISTER OPERATIONS    |        |               |      |      |             |          |       |

| BCF          | f,b   | Bit Clear f                 | 1      | 01            | 00ЬЬ | bfff | ffff        |          | 1,2   |

| BSF          | f,b   | Bit Set f                   | 1      | 01            | ОІЬЬ | bfff | ffff        |          | 1,2   |

| BTFSC        | f,b   | Bit Test f, Skip if Clear   | 1(2)   | 01            | ЮРР  | bfff | ffff        |          | 3     |

| BTFSS        | f,b   | Bit Test f, Skip if Set     | 1(2)   | 01            | ПРР  | bfff | ffff        |          | 3     |

| LITERAL AN   | ND C  | ONTROL OPERATIONS           |        |               |      |      |             |          |       |

| ADDLW        | k     | Add literal and W           | 1      | 11            | IIIx | kkk  | kkk         | C,DC,Z   |       |

| ANDLW        | k     | AND literal with W          | 1      | 11            | 1001 | kkk  | kkk         | Z        |       |

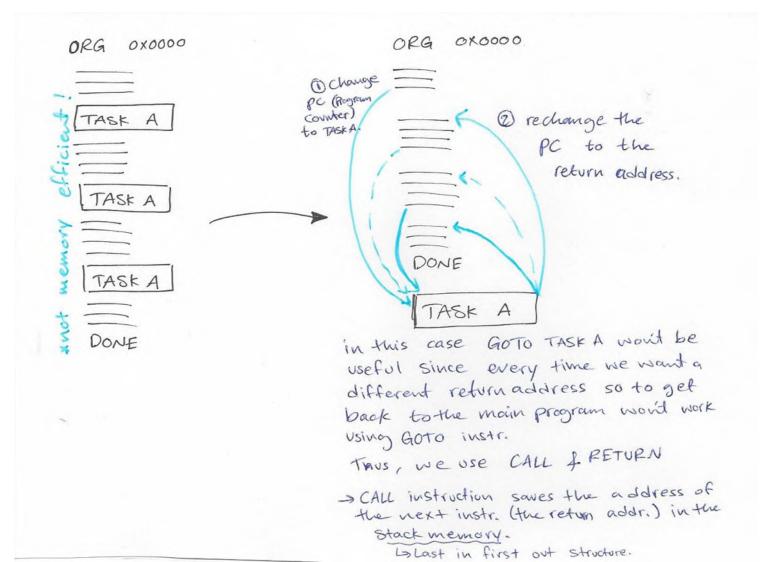

| CALL         | k     | Call subroutine             | 2      | 10            | 0kkk | kkk  | kkk         |          |       |

| CLRWDT       |       | Clear Watchdog Timer        | 1      | 00            | 0000 | 0110 | 0100        | TO.PD    |       |

| GOTO         | k     | Go to address               | 2      | 10            | lkkk | kkk  | kkk         |          |       |

| IORLW        | k     | Inclusive OR literal with W | 1      | 11            | 1000 | kkk  | kkk         | Z        |       |

Table A1.1 PIC 16 Series Instruction Set Summary-Cont'd

| Mnemonic, |   |                             |        | 14 Bit opcode |      |      |      | Status   |       |

|-----------|---|-----------------------------|--------|---------------|------|------|------|----------|-------|

| operands  |   | Description                 | Cycles | MSb           |      |      | LSb  | affected | Notes |

| MOVL      | k | Move literal to W           | 1      | 11            | 00xx | kkk  | kkk  |          |       |

| RETFIE    |   | Return from interrupt       | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW     | k | Return with literal in W    | 2      | 11            | 0lxx | kkk  | kkk  |          |       |

| RETURN    |   | Return from Subroutine      | 2      | 00            | 0000 | 0000 | 1000 |          |       |

| SLEEP     |   | Go into standby mode        | 1      | 00            | 0000 | 0110 | 0011 | TO.PD    |       |

| SUBLW     | k | Subtract W from literal     | 1      | 11            | 110x | kkk  | kkk  | C.DC.Z   |       |

| XORLW     | k | Exclusive OR literal with W | 1      | 11            | 1010 | kkk  | kkk  | Z        |       |

**Note 1**: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, ·1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d 1), the prescaler will be cleared if assigned to the Timer 0 module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

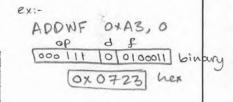

|                                 | e-oriented File register instructions: (18 inst) they process bytes in file registers.                                                  |              |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                                 |                                                                                                                                         | micros benue |

|                                 | ADDWF 0x20, 0<br>prode operand 1 operand 2                                                                                              | accessorie.  |

| the production is the factor of | -> ** the opcode is not case sensitive. ADDWF = add wf                                                                                  | -            |

| ap-1.                           | $0x20$ is a 7-bit address operand called (f): file reg. address operand ox $20 \equiv 0xA0$ because $0xA0$ has the same row as $0x20$ b | erand.       |

|                                 | with different bomk (bank 1). so, taking 7-bits only (ne                                                                                |              |

|                                 | bank selection bit) they'll look the same.                                                                                              | minimum.     |

| Op-2.                           | 0; is a 1-bit operand called (d) direction distination.                                                                                 | eneconomic   |

|                                 | L> 0 : Save in working reg.                                                                                                             | stanton-     |

|                                 | Ly 1: save in file reg. with address f (we can't specify another of since max. # of operand                                             | man Property |

- Introduction to PIC 16 ISA

- Types of operands

- A 7-bit address for a memory location in RAM (Register File) denoted by f

- A 3-bit to specify a bit location within an the 8-bit data denoted by b

- A 1-bit to determination the destination of the result denoted by d

- A 8-bit number for literal data or 11-bit number for literal address denoted by k

- Examples

- clrw

- · Clears the working register W

- clrf f

- Clears the memory location specified by the 7-bit address f

- addwff,d

- Adds the contents of the working register W to the memory location with 7-bit address in f. the result is saved in W if d =0, or in f if d = 1

- bcf f, b

- Clears the bit in position specified by b in memory location specified by 7-bit address f

- addlw k

- Adds the content of W to the 8-bit value specified by k.

The result is stored back in W

#### The PIC 16 Series Instruction Set

**Byte-oriented File Register Operations**

- Format: op f, d

- op: operation

- £: address of file or register

- d: destination (0: working register, 1: file register)

- Example: address label (this is case sensitive Port a + PORTA)

addwf PORTA, 0

Adds the contents of the working register and register PORTA, puts the result in the working register.

9

#### **Bit-oriented File Register Operations**

- Format: op f, b

- op: operation

- f: address of file or register

- b: bit number, 0 through 7

- Example:

bsfSTATUS, 5

Sets to 1 Bit 5 of register STATUS.

-sat 03H & 83H

11

#### The PIC 16 Series Instruction Set

#### **Literal and Control Operations**

- Format: op k

- op: operation

- k: literal, an 8-bit if data or 11-bit if address

- Examples:

addlw 5

Adds to the working register the value 5.

call 9

Calls the subroutine at address 9.

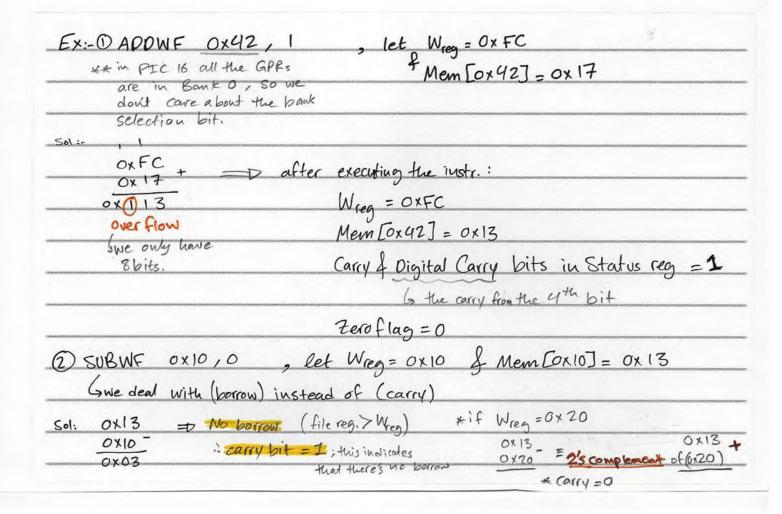

#### **Arithmetic Instructions**

| N | Vinemonic | Operands | Description             | Cycles | Status<br>Affected |

|---|-----------|----------|-------------------------|--------|--------------------|

|   | ADDWF     | f, d     | Add W and f             | 1      | C,DC,Z             |

|   | COMF      | f, d     | Complement f            | 1      | . Z                |

|   | DECF      | f, d     | Decrement f             | 1      | carry Z            |

|   | INCF      | f, d     | Increment f             | 1      | affected Z         |

| 2 | SUBWF     | f, d     | Subtract W from f       | 1      | C,DC,Z             |

|   | ADDLW     | k        | Add literal and W       | 1      | C,DC,Z             |

| V | SUBLW     | k        | Subtract W from literal | 1      | C,DC,Z             |

w is always the subtractor (after -)

d = 0, result is stored in W d = 1, result is stored in F

13

| <u>s</u> ) (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | let STATUS = 0 × 0A , Mem[0 × 31] = 0 × FF , Wreg = 0 × 00 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Service Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INCF 0x31,0                                                |

| NOWINGSON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OXFF+1 = 0x00 (with overflow)                              |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | fter execution:                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Wreg = 0x00                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mem[0x31] = OXFF                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STATUS -> carry & DC arent affected.                       |

| NUMBER CO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Zero bit = 1                                               |

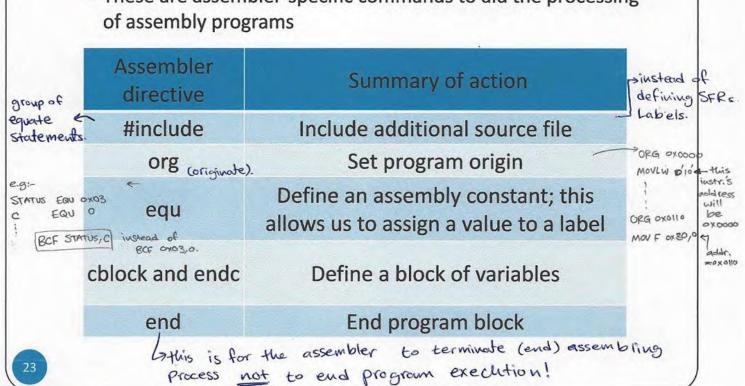

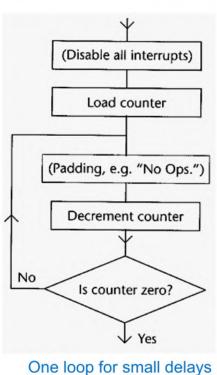

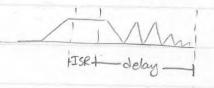

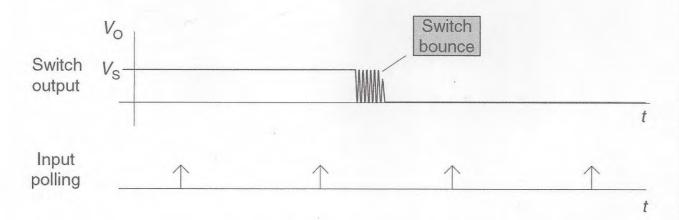

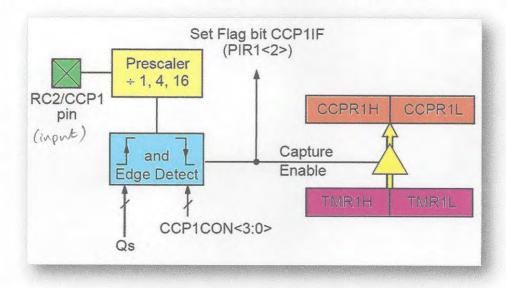

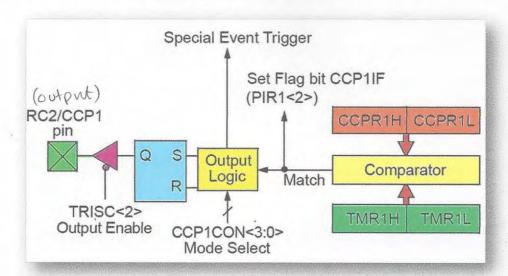

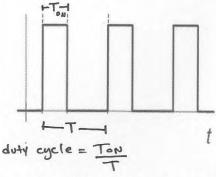

| one year                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | : STATUS = OXOE                                            |