28

#Power\_Unit

9

The University of Jordan

Faculty of Engineering & Technology

**Computer Engineering Department**

**Digital Electronics**

Fall 2014 / Midterm Exam

Student Name: #fower\_DAIR Student Number: 0903261

Olar all republies 0100576

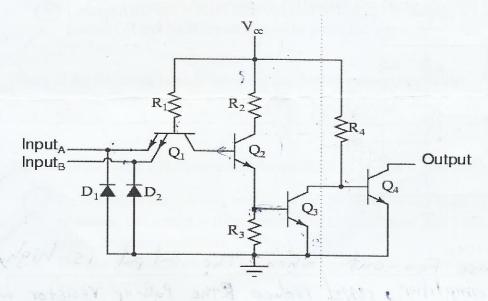

Consider the following circuit and answer the questions below

Draw the truth table of the gate.

| <b>6</b> |   |   | and the same |   |

|----------|---|---|--------------|---|

| 4        | Α | В | Output       | ~ |

| IØ       | 0 | 0 | 0/           |   |

| 16       | 0 | 1 | 0/           | 1 |

| 16       | 1 | 0 | 0 /          |   |

| 0        | 1 | 1 | 1/           |   |

What is the function of the gate?

AND

VA. VB

What is the effect of the following actions?

| action                                                 | effect                                                                 |

|--------------------------------------------------------|------------------------------------------------------------------------|

| remove Q4 and take the output from the collector of Q3 | The Circuit will be mano" Grate                                        |

| remove R3                                              | Or will enter saturation faster                                        |

| increase R3                                            | reduce the switching time from (1->0), Q3 will enter saturation faster |

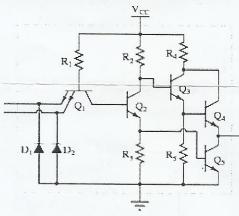

Consider the following circuit and answer the questions that follow:

The function of Q4 is:

In crease Fan - out when the ont put is high,

Current amplifier, and reduce 18 the Pull-up resistor when we

The ontput switch from 0 > 1 (reduce Propagation delay)

make sure That Q5 and Q3 will not be on together

Phase splitter consists of:

Q2, R2. R3

Totem pole consists of:

Q3, Q5

| What are the voltages of logic one an | logic zero in standard ECL gates ( | that was covered) |

|---------------------------------------|------------------------------------|-------------------|

|---------------------------------------|------------------------------------|-------------------|

Vo"=-1.58

Vans = 6.76

How many outputs each ECL gate usually has

2- outputs

What should be done to unused inputs on TTL gates?

+XB=X+BDED-

1. They should be left disconnected so as not to produce a load on any of the other circuits and to minimize power loading on the voltage source.

All unused gates should be connected together and tied to  $V_{CC}$  through a 1 k  $\Omega$  resistor.

3. All unused inputs should be connected to an unused output; this will ensure compatible loading on both the unused inputs and unused outputs.

4. Unused AND and NAND inputs should be tied to  $V_{CC}$  through a 1 k  $\Omega$  resistor; unused OR and NOR inputs should be grounded

Which of the following logic families has the shortest propagation delay?

1. CMOS 2. BiCMOS 3. ECL 4. 74SXX

What is unique about TTL devices such as the 74SXX?

These devices use Schottky transistors and diodes to prevent them from going into saturation; this results in faster turn-on and turn-off times, which translates into higher frequency operation.

2. The gate transistors are silicon (S), and the gates therefore have lower values of leakage current.

3. The S denotes the fact that a single gate is present in the IC rather than the usual package of 2–6 gates.

4. The S denotes a slow version of the device, which is a consequence of its higher power rating.

What is the major advantage of ECL logic?

| 1) very high speed | 2. wide range of operating voltage |

|--------------------|------------------------------------|

| 3. very low cost   | 4. very high power                 |

The term buffer/driver signifies the ability to provide low output currents to drive light loads.

1. True (2.) False

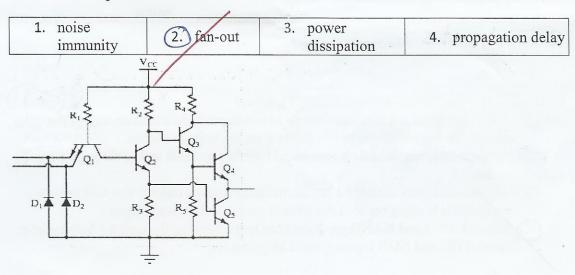

Ten TTL loads per TTL driver is known as:

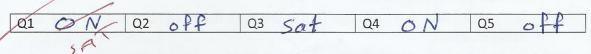

Using the schematic diagram of a TTL NAND gate, determine the state of each transistor (SAT, ON or OFF) when all inputs are high.

If all inputs to a TTL NAND gate are low, what is the (SAT, ON, OFF) condition of each transistor in the circuit?

Assuming that one input is disabled and the second input increases from 0V to 5 V. write the sequence of states through which transistors Q2 and Q5 go through ( OFF, ON and SAT).

| 1000000000 |      |        |          |

|------------|------|--------|----------|

| Q2 0       | > h  | Q5     | Sat      |

|            |      |        |          |

|            | Q2 c | Q2 0 N | Q2 ØN Q5 |

Which of the following summarizes the important features of emitter-coupled logic (ECL)?

low noise margin, low output voltage swing, negative voltage operation, fast, and high power consumption

- good noise immunity, negative logic, high-frequency capability, low power dissipation, and short propagation time answer is (b)

- c) < low propagation time, high-frequency response, low power consumption, and high output voltage swings

- poor noise immunity, positive supply voltage operation, good low-frequency operation, and low power

Totem-pole outputs <u>can</u> be connected <u>in parallel</u> because <u>some times</u> Ligher Convent can, in parallel, sometimes higher current is required.

can, in parallel, sometimes higher current is required

cannot, together, if the outputs are in opposite states excessively high currents can damage one or both devices

should, in series, certain applications may require higher output voltage can, together, together they can handle larger load currents and higher output voltages

A TTL totem-pole circuit is designed so that the output transistors

| 1. are always on together |                | provide linear phase splitting |                 |        |

|---------------------------|----------------|--------------------------------|-----------------|--------|

| 3. provide voltage re     | age regulation |                                | ver on together | answer |

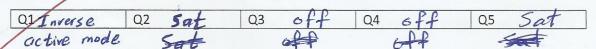

35. Fan-out is determined by taking the Smaller result(s) of Total

| 1. smaller, $\frac{I_{OL}}{I_{IL}}$ or $I_{oh} = \frac{V_{OH}}{R_{OH}}$ | 2. larger, $\frac{I_{OL}}{I_{IL}}$ or $\frac{I_{OH}}{I_{IH}}$  |

|-------------------------------------------------------------------------|----------------------------------------------------------------|

| 3. smaller, $\frac{I_{OL}}{I_{IH}}$ or $\frac{I_{OH}}{I_{IH}}$          | 4. average, $\frac{I_{OL}}{I_{IL}}$ or $\frac{I_{OH}}{I_{IH}}$ |

From the following specifications determine the fan-out for the logic family.

$I_{OL} = 32 \text{ mA}$   $I_{IL} = 2 \text{ mA}$

| <ol> <li>HIGH state is 16, LOW state is 8</li> <li>HIGH state is 4, LOW state is 8</li> </ol> | 2 HIGH state is 8, LOW state is 16 4. HIGH state is 8, LOW state is 4 |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                                                                               | state is 6, LO W state is 4                                           |

The TTL HIGH level source current is higher than the LOW level sinking current.

Consider the following circuits. Determine the logic function of each of them

0

What is the effect of increasing  $\beta$  on the fan-out ( in the last circuit)

Increasing Fan-out