## DIGITAL ELECTRONICS NOTEBOOK BY: ABDELJABBAR SUWWAN

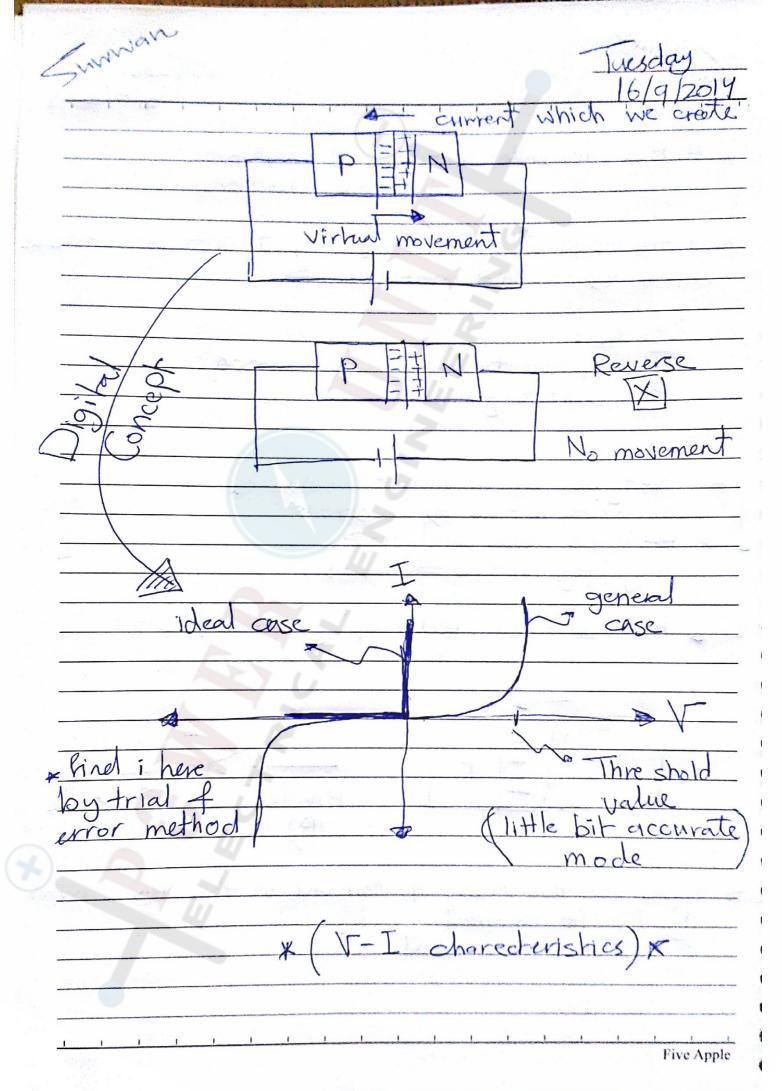

| Survivan                                                                                                          | Tuesday<br>16/9/2014             |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------|

| * Adiuc elements: diode, train do amplifi                                                                         |                                  |

| * if the input effects on the outp                                                                                | ut with a variable               |

| Diode:  [] Amplification (application)  [] Switching                                                              | utions)                          |

| M-type semi conductor (doc<br>majority is -ve => electrons<br>x P-type semi conductor<br>majority is tre => holes |                                  |

| Doin of Them to coping                                                                                            |                                  |

| A there are two types of current                                                                                  | e Cathode (N) in the PN junction |

| Difusion current                                                                                                  | Five Apple                       |

Survivor Tuesday vollage Shifter If there is a threshold value (general case we will get a shift in the signal, like = threshold value the AC value MHOW to get OR, AND gates: ⇒OR-gate Scanned by CamScanner

Zwwar \* A problem with the diode is whom its of output, it is less than level of that will cause a problem in digit be used IOK

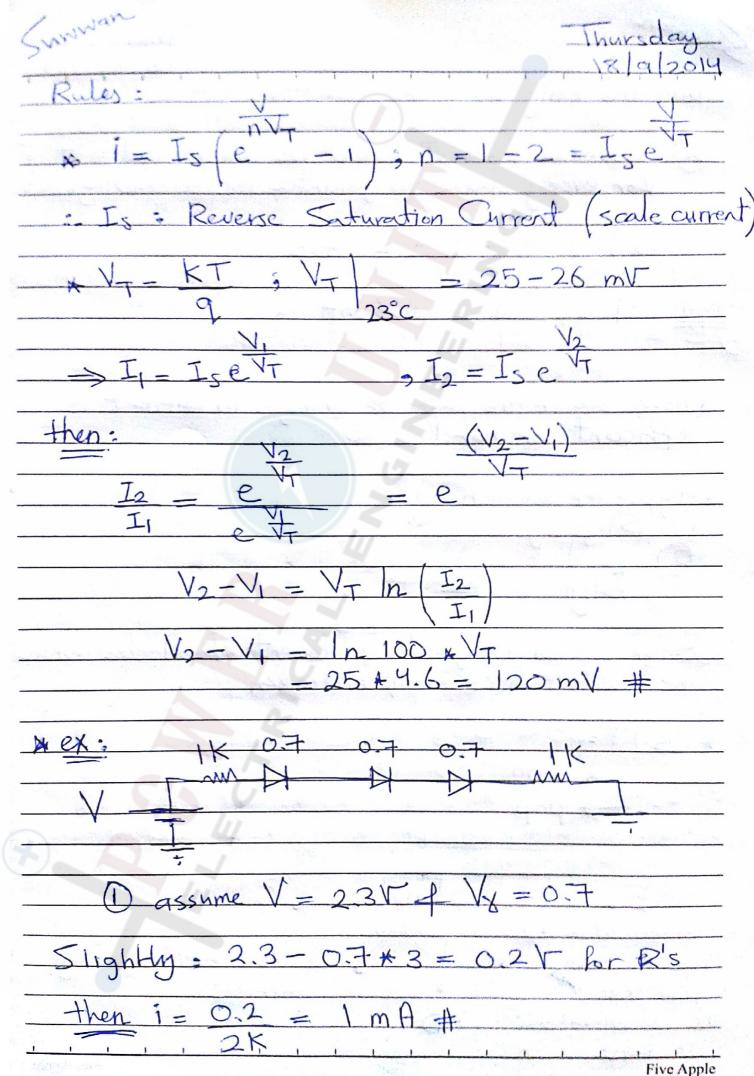

| Survivar Thursday<br>18/9/2014                                                       |

|--------------------------------------------------------------------------------------|

| for the fully =                                                                      |

| assume V=10V, and we must add a 0.1V for every diode to gurantee the conducting, so: |

| helly: 10-2.4 = 7.6                                                                  |

| $\frac{1}{2} = \frac{7.6}{2} = 3.8 \text{ mA} + \frac{1}{2}$                         |

| efficient or not.!                                                                   |

| Slightly :                                                                           |

| 2) Good 3) Pully                                                                     |

| re need to use multiple diades.                                                      |

| * BJT=                                                                               |

| $\rightarrow \rho \rho \rho$                                                         |

| E on pin C                                                                           |

| here is much letections are majority higher than a carriers the concentration B      |

| in base                                                                              |

Summer Five Apple

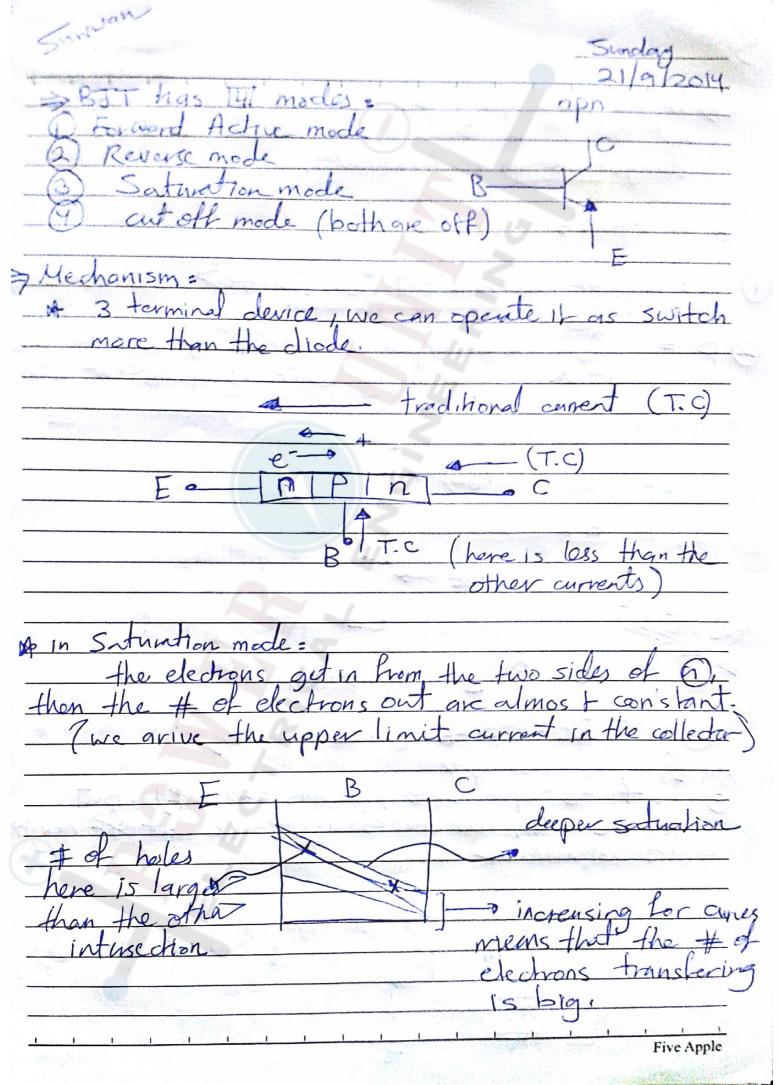

Survan Sunday 21/9/2014 the Tr. value of it is more than 0.6 V, it is acholy K to find the input voltage, assume that:

RB = 10K, RC = 10K & B = 100 0.7 V BC(ON) = 0.4 V OE (SAT), = 0.35 V \* VBE (SAT) A when Vi is smaller than 0.7 that morns the output will be Vec. - VCE(SAT) = Q.IV A VCE(SAT) = 0.2V

Gravian Tuesday 23/9/2014 suppose: achial W=0.85 this point will shift to the left if Ic increased, and to night if it declared 0.2 or 0-1 Rb+0.8 (depends on VDF and if we increase Vcc - 0.35 Rc Ro will take it If we decrease it will VRb = Ib. Rb V: - VRb + 0.8 > For explains (x) up: Vi has avange of (0.1 - Vcc) this cet is an (inverter), coz when we give a

Vi = 0 -> 0.7 (mouns logic [0]) so the output is

Vcc (means logic [1]), and if V; more than 0.7 mains logic []] we suppose Vo is zero (means Five Apple

Survan if of = 0.5 in out ex > deep sa \* noise margin : 0 0 Scanned by CamScanner

Thursday \* Suppose that so the all noise value = worst one coz we can't predict the noise \* Capacitor makes delay to switching time. types of gates work on bipolas : RTL Registor - Transistor DTL Diode - Transiston Transistor - Transitor Emitter Coupled logic a Rip coz shifting left ornight, its effecting or gets the saturation made. \* Transistor is grounded, means it always be of. equal to 0-8V. Five Apple

Chronel For the NoR gate which he disigned:

If Rb = 2010, If the other Tr is off: Re DO -0.7 0.1-0.7 but, if we cascade of the Transistor Five Apple

Summan Thursday 25/9/2014 numbered gates similar gates can be ched without effecting the functionality. Vac Vcc Vcc Five Apple Scanned by CamScanner

Sympart Sunday 28/9/2014 Wollage Swing: - Lange of the vollage of the output (Def.) - Increasing of vollage swing there is problemin noise of Folerance à noise as ( DO of DI) - (noise immunity) - advantage - (switching time) - dis adventage replace this - Current hagging (effect on the Can-out) must be large disadvantage x for RTL: if R1 = 45052/ Rc = 640.52: if we are increasing the resistors, the level of current will be decreased, so we decreased the power dissipation -The we conscaded the boto other RTL cktos, we will increase the switching time (horse)

Scanned by CamScanner

if the diodes are low, the owner will not reach the Try, so ithe Vo will be equal to but, if the diades are high, the current will pass the diade of recistor and go to the Tr. 1 so the Tr will be saturated, and Va will be - this gate is VIV2 and its called (NAND) - if we connected diodes on the Volike this: Coz the diade active from -ve side fits get low. - Fan out of RTL calculated on () of in DT , there is strong limitations on the - VB is equal to -2V, so more number of voltage supplies is disadvantage.

- VB is -2 we will increase the speed of hemoval charges & less resistance on the same line too (from 0 -> 1) Pasksh

Summan Synday 28/9/2014 \*Voltage Swing: - range of the vollage of the output (Del) - increasing of voltage swing there is problem in noise & Folerance ; noise as (AO f DI) 9 - (noise immunity) - adventage - (switching time) - dis advertage replace this cct by capacitor - Current hogging (ellect on the Can-out) disadvantages must be large phor RTL: if Rb= 4502, Rc= 640, SL: - if we are increasing the resistors, the level of current will be decreased, so we decreased the power dissipation - If we ascaded the 16 to other RTL cktes, we will increase the switching time (morse)

Vo will increase the switching time (morse)

Vo will increase the switching time (morse)

Five Apple L-MM-11-0

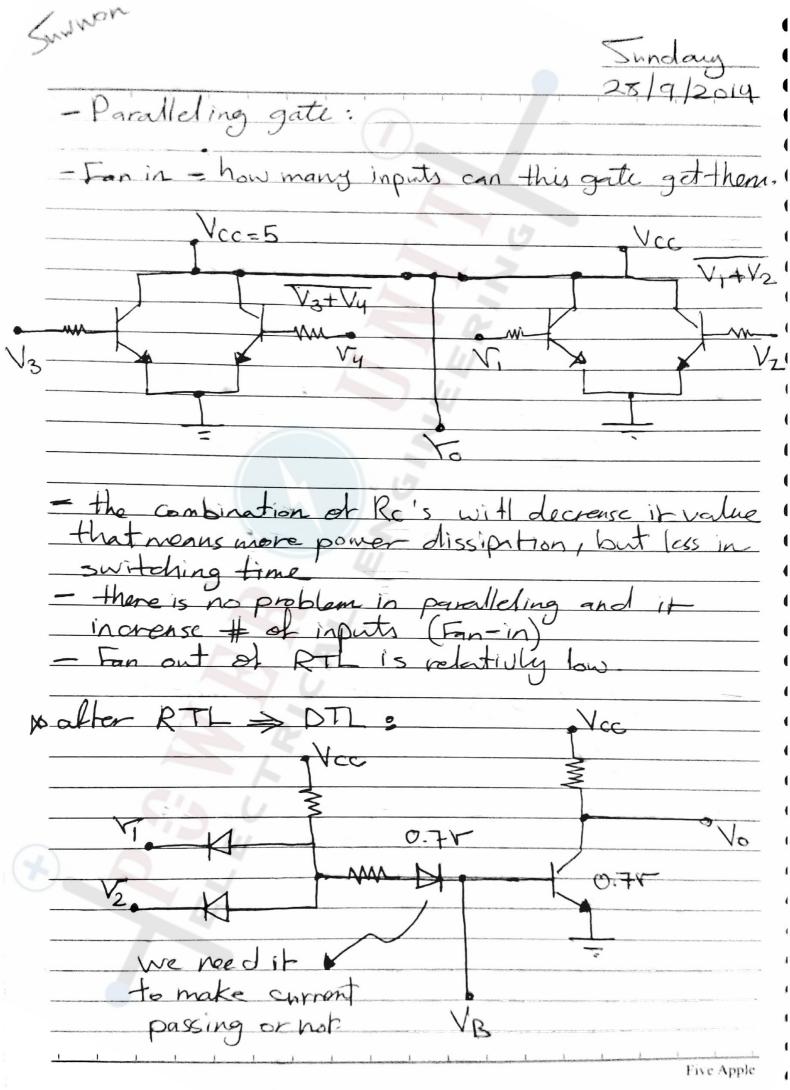

Summon Sunday = 25/9/2014 = - Paralleling gate: - Fan in = how many inputs can this gate get them. V3+V4 Wy V4 - the combination of Rc's will decrease it value that means more power dissipation, but less in switching time - there is no problem in paralleling and it increase # of inputs (Fan-in)

- Fan out of RTL is relatively low. patter RTL > DTL : we need it & to make chron passing or not Five Apple

Sunday - if the diodes are low, the current will not reach the Tr. , so ithe Vo will be equal to Vcc.

but, if the disdes are high, the current will

pass the disde of resistor and go to the Tr. 1

so the Tr will be saturated, and Vo will be - This gate is VI-V2 and its called (NAND) - if we connected diodes on the Volike this: So the concent will pass into diodes, Coz the diade Tr. is Saturated active from -ve side fits get low. - Fan out of RTL calculated on (1) of in DT calculated on (0) - in DTL, there is strong limitations on the Fan out. - VB is equal to -2V, so more number of voltage supplies is disadvantage. - VB is -2 we will incrouse the speed of removal charges of less resistance on the same line too (from 0 - >1) Paskesh Five Apple

SIMVAR Luesday 30/9/2014 A Ro P VB are used for optimization For the DTI: I don't need to provide current when I'm high to the driven gates

- but in the RTL, I have to provide it \* when the gate has an output zero; the current will go into it of the opposite is correct. -> for agood design / B >- ve fits R > low. CKL SRJ the time rooded for transfer from (1) to (2) called Storage time. speed of transition is last as possible as we can Five Apple

Surwar hesday because I want the \* decross R, means deep sating Moving to the base so for the (x) above, if the V, flz are zeros, you can't open the diodes D, of the other one in the Transistor mode slowly, but it it has a low value, that mans you need a small correct in this branch, so a big sat laster Five Apple

Somwan Vcc Dell down passing junctionabove is off what is the output? down charge =>it is very slow, why ?! because its got alot of currents for # diodes Collecter Current Five Apple Chrient

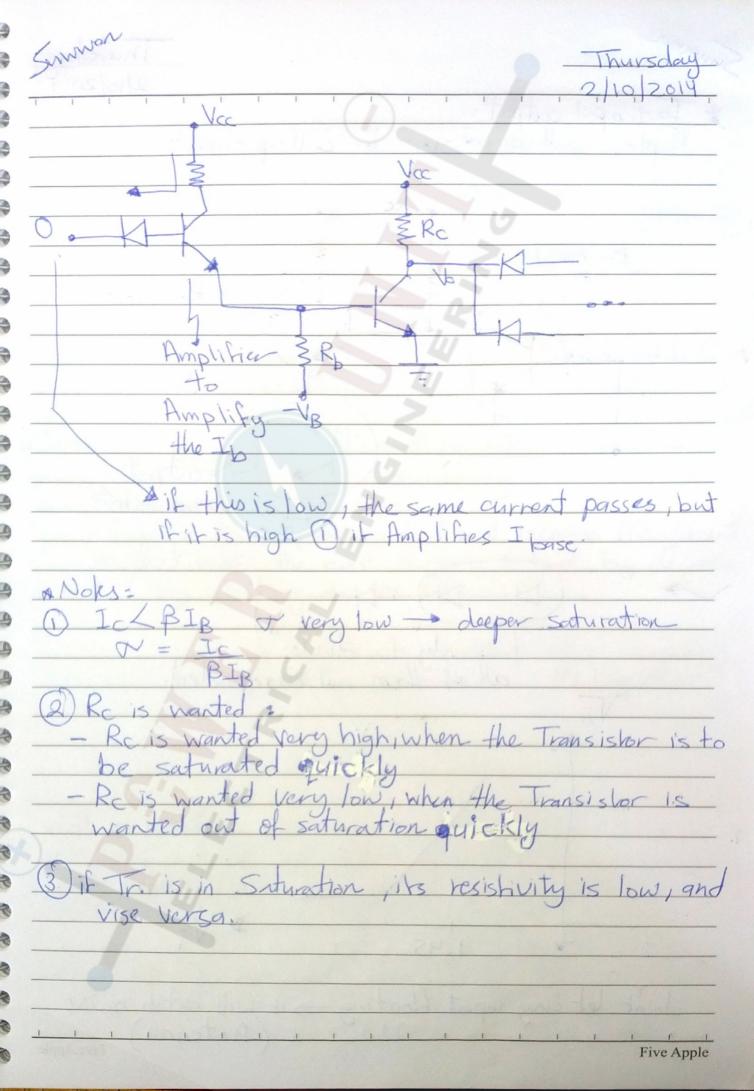

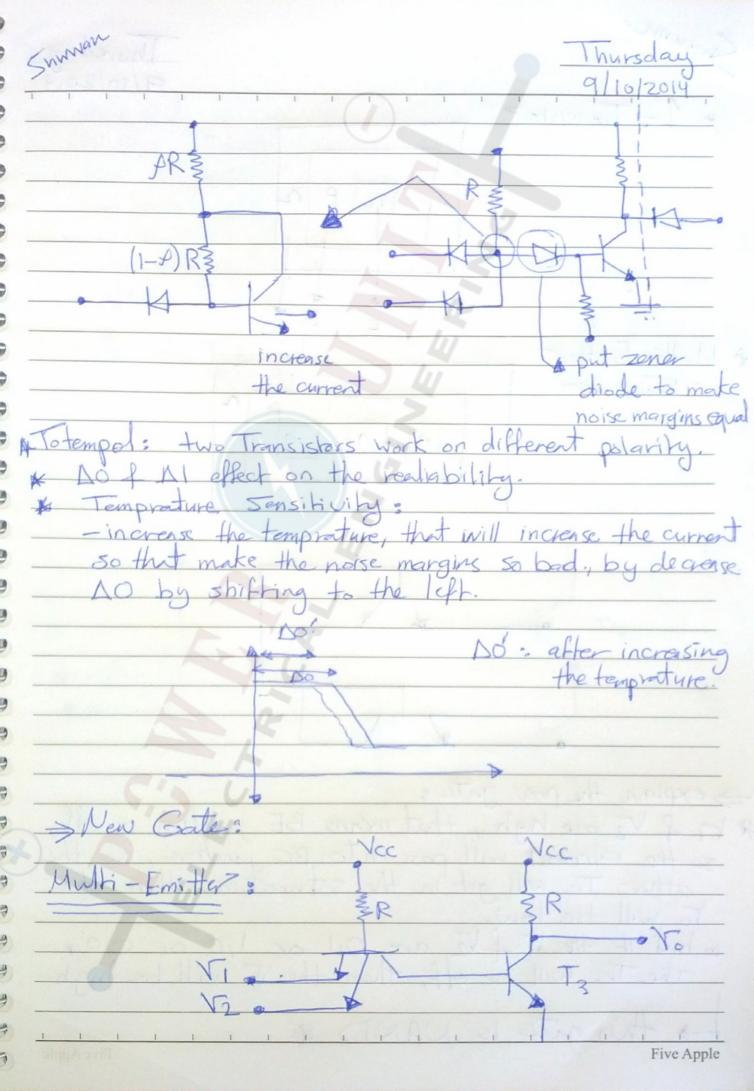

Thursday 2/16/2019 Summer \* To tempol output: Replace pull up resistor pull up arant to inver Resistor two diodes 45 don't let any input floating -it will atch noise (Antenna)

Grunar Thursday A Multi- Emitter Transistor > explain the prev. gate: A ty & Vz are high, that means BE junction is oft, so the current will pass into BC junction, so the other Tr. will get in the saturation, then the to will be low. so but if the VI & VI are 0,1 or 1,0 or 0,0, The Tr. will be off, then the Vo will be high. 4 \* this get IS NAND \* Five Apple

Suwvar Thursday this gate solving the problem of switching and its very attractive, comparing with the DTL that has a branch pulls a current. Is in the gate the transfering from on to off or - For this gate the Fan out is limited until we get out from the saturation. - for the Totempol: we can get in the saturation

f get out fromit very

quickly. # phase spliter \*

high from terminal and low from other gurantee that if the T3 is on so Ty is off, to

gurantee the principle of totempol.

Five Apple

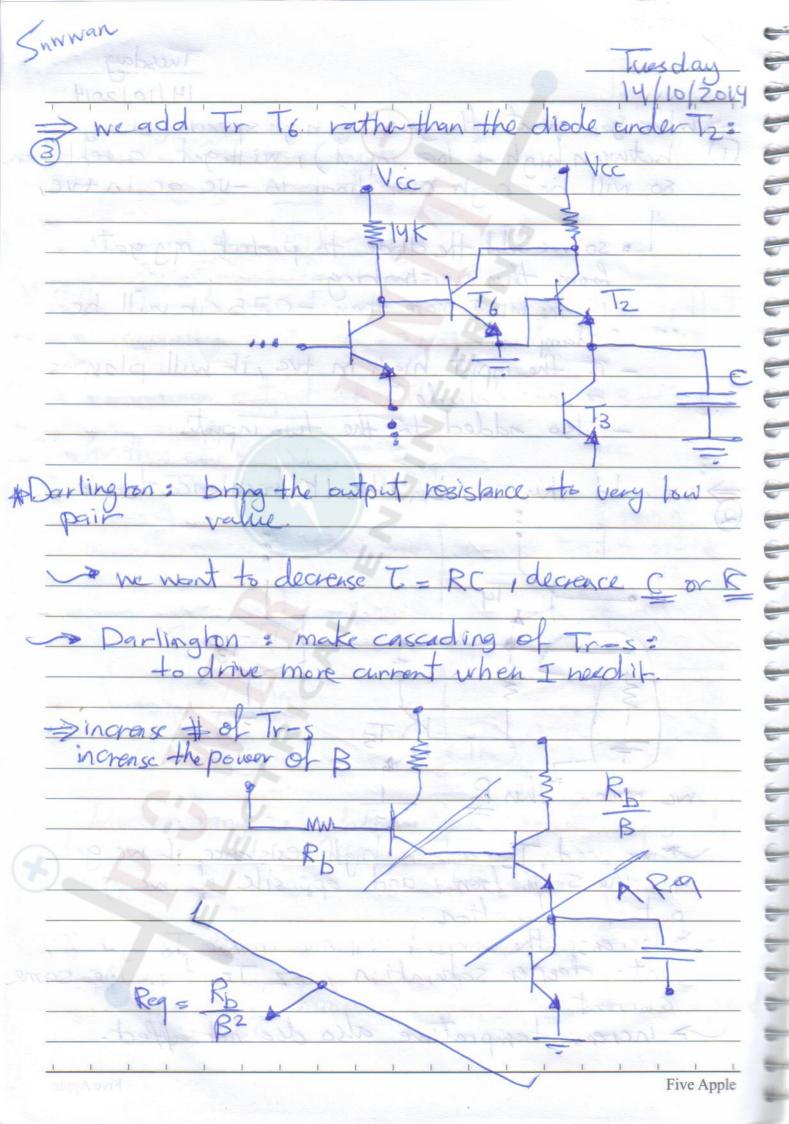

Sindery > we transfer from DTL -> TTL because the

Switching time. 12/10/2014 the saturation 1-0 Rc as low as possible ( because T = RC the Capacitance (C) appears in 3 sources:

- (D) junction in Tr.

- (D) between Vo 1 the ground

- (B) when the Vo line go to Similar Tr-s. situration (Increase the active region) phases (polarities) - and if Vi decrenses, Vo or RE decreuses, and

I To on Re will be increased.

Five Apple

Jcc 1802 vollage Five Apple Suman current Vcc 14 K speed. hundreds of KA => make speed Five Apple

Sunwan Thesday when you operate the gate & high speed so we add the diade to protect my gate the input more than -0.75 it will the input high in tre, i this Tr. by the 1K resistance too & as high resistance if we get e correct will not deeper saturation temprature also does not affect. Five Apple

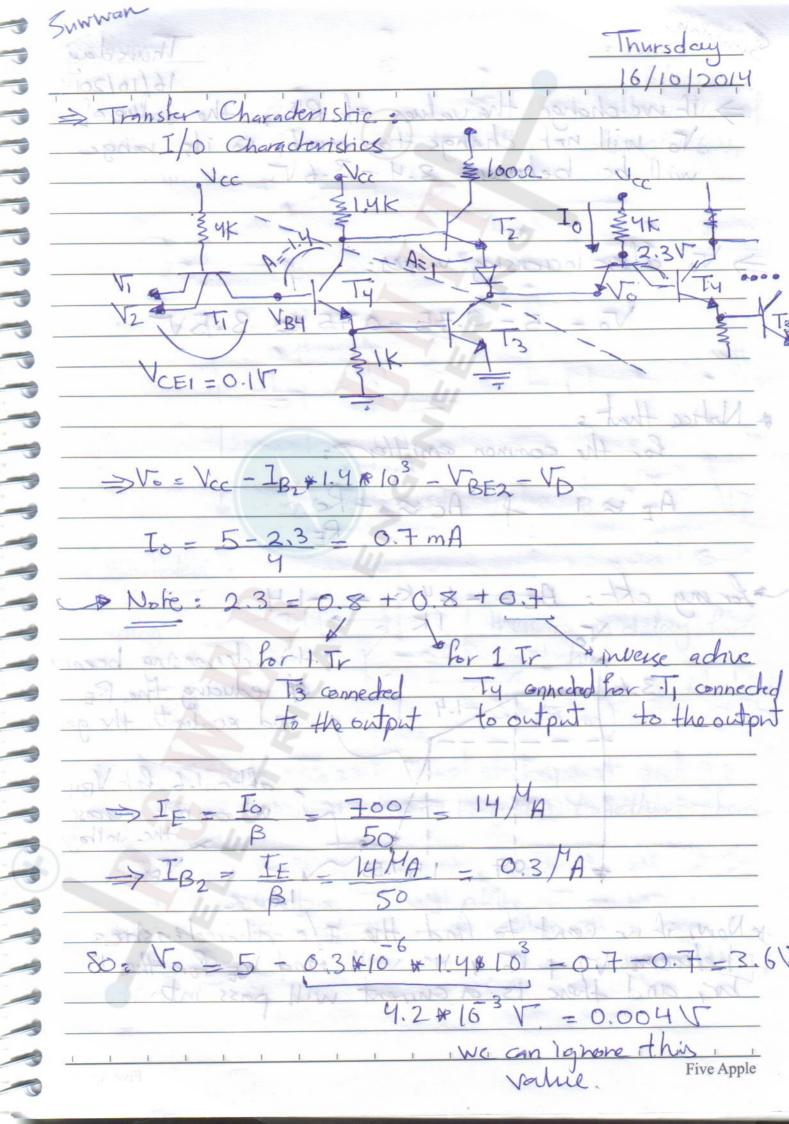

Thursday > if we change the values of R's, the value of Yo will not change too much, so its range will be between 3.4-3.6 V. > To after increasing values: Vo - 5 - 0.75 - 0.75 × 3.5V Notice that;

for the common emitter; AE SI ACS - RC

ANTO RESS-Z-J For my ckt: Ac = -1.4k = -1.4 this decreasing because of reducing the RE o.7 1.51.55

After L6 for VB4

We can not increase

the voltage \* Now, if we want to find the I/o charedinstics between Vift to I we will kind Vot for the 1st Er, and there is a current will pass into it Five Apple

Shwwan Mursday lique, we must subtract all values Vi will not stop a 075 0.8 \* Shoteley there is no delay for damping Switching Cincrasing switching junction doesn't open Colle deix gate Five Apple

Suman unday if this input effect on this chr. additional input) a like: mont \* but if the input is low, The Transistors which I put a circle on them are always off. shor the chr above, there is a version put Shotely instead of Tr., Neither T because it will not go in the saturation by configurion of the dosign. Five Apple Five Apple

, directions of current depend Input x Voltage range for the input ? the input from another gate. VCE -- 0.5 Five Apple

VC2 0.5V \* if the inputs are equal => Fhat means in @ the end of the active region the voltage on any side of will disable the other side. increasing Viz to 14: = 1.35 - so the Tr and this is the edge between ontoff active region-So: if we increase 19, by 4 To co.1 Vor will decrose, coz the curren pass, and Vez will increase

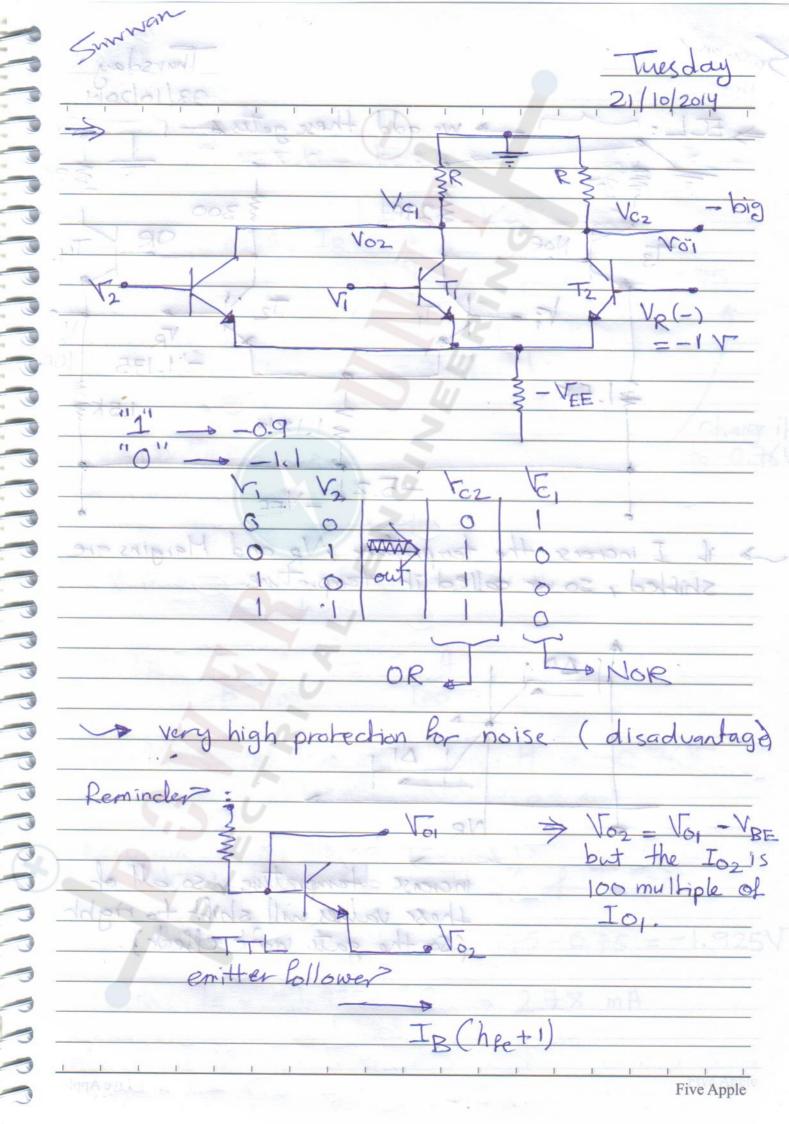

these getes 300 ₹290 300 OR NOR 1.5K Margins gre NR gate won't Five Apple Five Apple

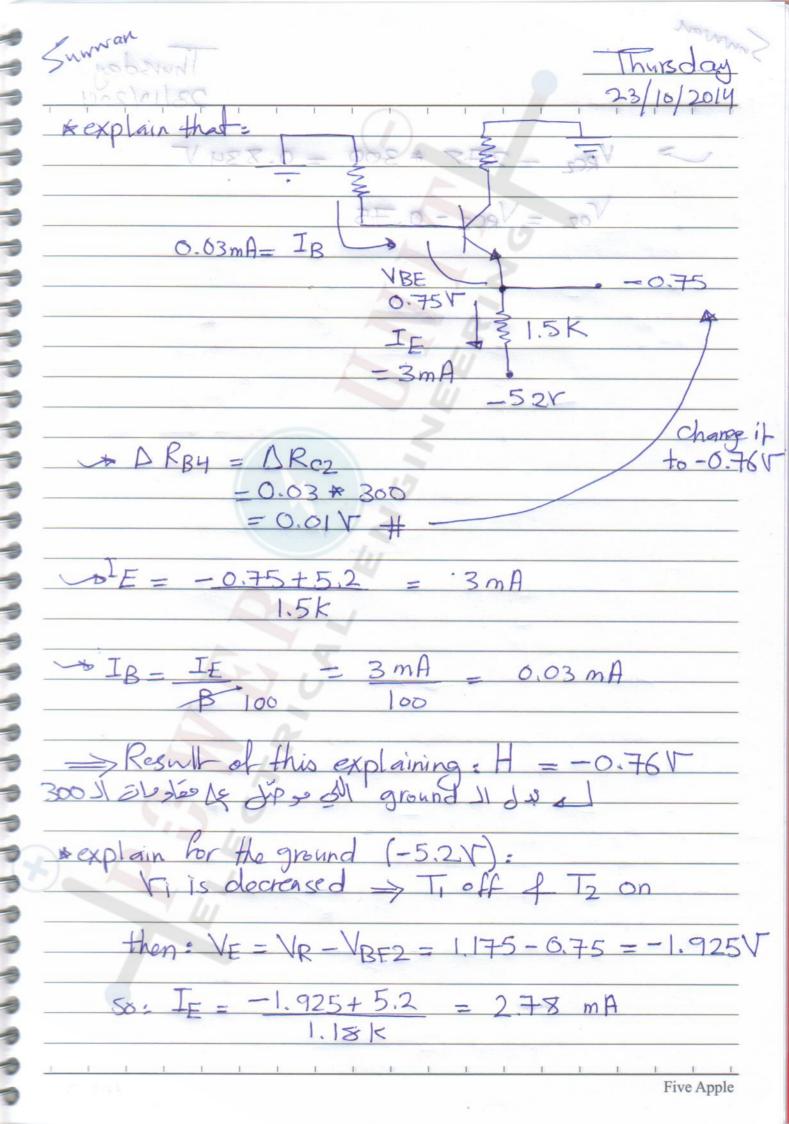

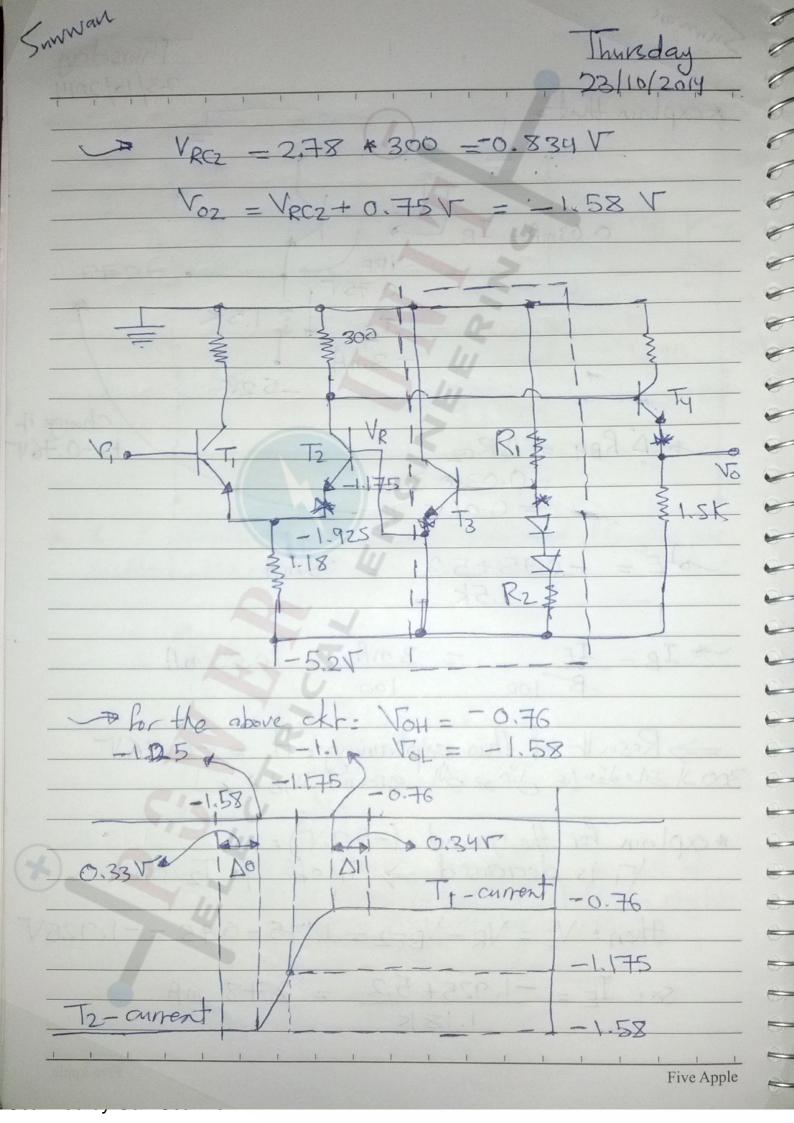

Sowwar Thursday 23/10/2014 MIDELOUITER 00 -1.925+5.2 Five Apple

Summan Sunday 26/10/2014  $I_{E_1} + I_{E_2} = I = constant$   $V_i - V_E)/V_T$   $V_R - V_E)/V_T$ take ratio: IEI = e(VR-VE)/VT then? IEI = e(VBI-VR) VT 1 95 = e (VBI-VR)/VT 5 .. DVB1 = 150 mV = 6VF you must take care about environment, and it is hard when we build the Tr. but one benfit that they are equal. I the values of voltages for the limits of margins must be constant too. > AV junction = -K AT # Five Apple

Five Apple

-5.2V

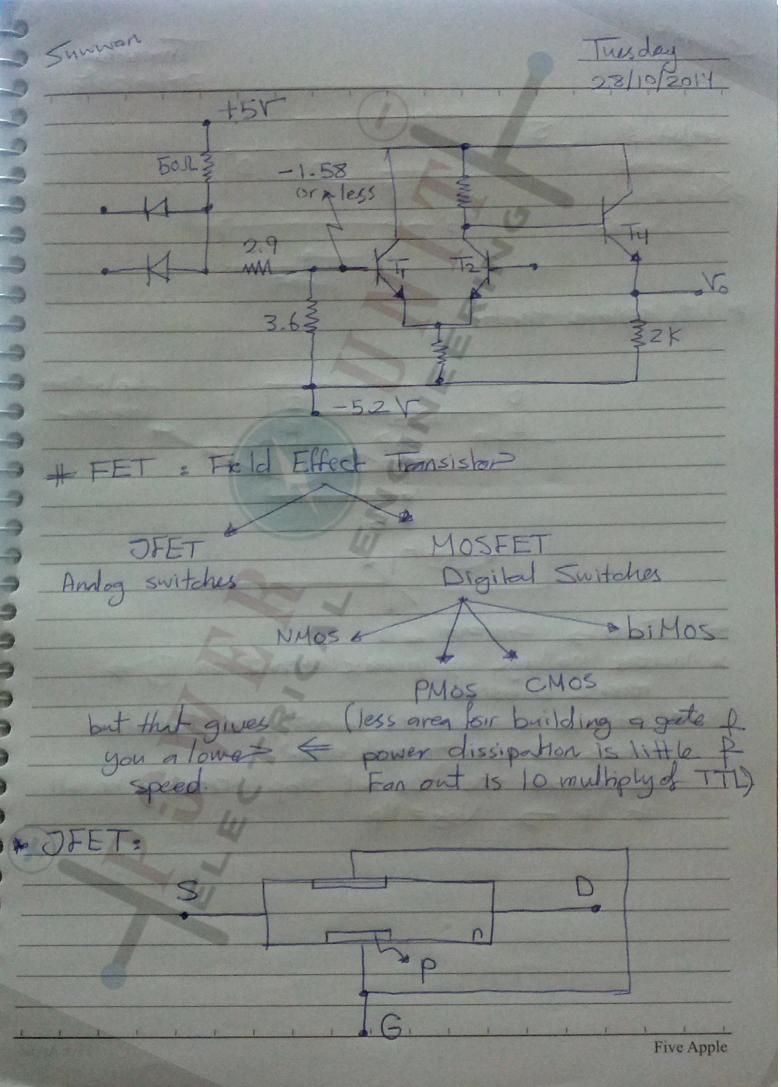

Suman & for the liquire () , and before the temprostiture changes: 5.2-0.75 -0.75) Ri AV = 25 p R, i vollage division \* Translation = is to imply the same logic of ECIL non-saturated logic | ECL -Five Apple

Suman ourrent العطارية بكونا \* lets explain dep leution 5 V=0 > current \* increase vallage => increase current on reverse bigsed. continue increasing the current, the depleation regions will open on each other the moment the VDS will stop increasing we call it Vp >> Vps = Vp Five Apple